概览

描述

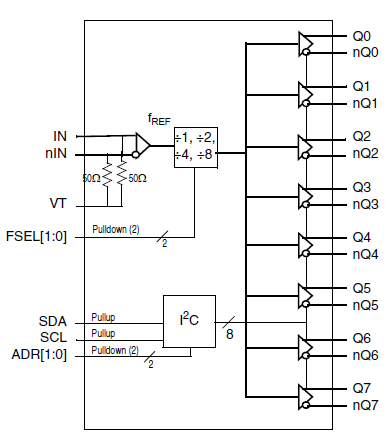

The 8T73S208 is a high-performance differential LVPECL clock divider and fanout buffer. The device is designed for the frequency division and signal fanout of high-frequency, low phase noise clocks. The 8T73S208 is characterized to operate from a 2.5V and 3.3V power supply. Guaranteed output-to-output and part-to-part skew characteristics make this device ideal for those clock distribution applications demanding well-defined performance and repeatability. The integrated input termination resistors make interfacing to the reference source easy and reduce passive component count. Each output can be individually enabled or disabled in the high-impedance state controlled by an I²C register. On power-up, all outputs are enabled.

特性

- One differential input reference clock

- Differential pair can accept the following differential input levels: LVDS, LVPECL, CML

- Integrated input termination resistors

- Eight LVPECL outputs

- Selectable clock frequency division of ÷1, ÷2, ÷4, and ÷8

- Maximum input clock frequency: 1000MHz

- LVCMOS interface levels for the control inputs

- Individual output enable/disabled via the I²C interface

- Output skew: <60ps

- Output rise/fall times: 350ps (maximum)

- Low additive phase jitter, RMS: 0.182ps (typical)

- Full 2.5V and 3.3V supply voltages

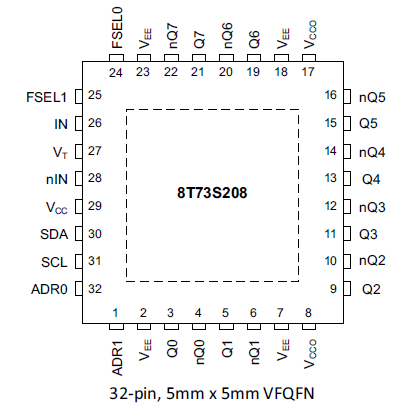

- Available in a lead-free (RoHS 6) 32-lead VFQFN package

- -40 °C to 85 °C ambient operating temperature

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的产品,查找 SamacSys 中的原理图符号、PCB 足迹和 3D CAD 模型。点击产品选项表中的产品,查找 SamacSys 中的原理图符号、PCB 足迹和 3D CAD 模型。

产品选项

当前筛选条件