概览

描述

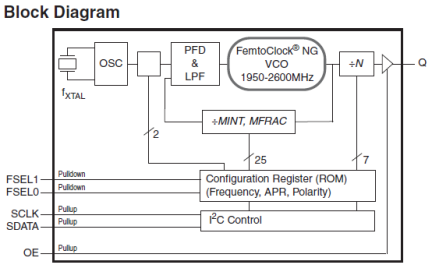

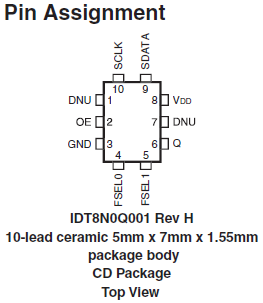

The 8N0Q001 is a quad-frequency programmable clock oscillator with very flexible frequency programming capabilities. The device uses Renesas' fourth-generation FemtoClock®NG technology for an optimum of high clock frequency and low phase noise performance. The device accepts 2.5V or 3.3V supply and is packaged in a small, lead-free (RoHS 6) 10-lead ceramic 5mm x 7mm x 1.55mm package.

Besides the four default power-up frequencies set by the FSEL0 and FSEL1 pins, the 8N0Q001 can be programmed via the I2C interface to output clock frequencies between 15.476MHz and 260MHz to a very high degree of precision with a frequency step size of 435.9Hz ÷ N (N: PLL post divider). Since the FSEL0 and FSEL1 pins are mapped to four independent PLL M and N divider registers (P, MINT, MFRAC, and N), reprogramming those registers to other frequencies under control of FSEL0 and FSEL1 is supported. The extended temperature range supports wireless infrastructure, telecommunication, and networking end equipment requirements.

特性

- Fourth generation FemtoClock® NG technology

- Programmable clock output frequency from 15.476MHz to 260MHz

- Four power-up default frequencies (see part number order codes), re-programmable by I2C

- I2C programming interface for the output clock frequency and internal PLL control registers

- Frequency programming resolution is 435.9Hz ÷ N

- One 2.5V, 3.3V LVCMOS clock output

- Two control inputs for the power-up default frequency

- LVCMOS/LVTTL compatible control inputs

- RMS phase jitter at 156.25MHz (12kHz to 20MHz): 0.250ps (typical)

- RMS phase jitter at 156.25MHz (1kHz to 40MHz): 0.290ps (typical)

- 2.5V or 3.3V supply

- -40 °C to 85 °C ambient operating temperature

- Available in a lead-free (RoHS 6) package

产品对比

应用

文档

|

|

|

|

|---|---|---|

| 类型 | 文档标题 | 日期 |

| 数据手册 | PDF 707 KB | |

| EOL 通告 | PDF 761 KB | |

| 手册 - 硬件 | PDF 182 KB | |

| 产品简述 | PDF 6.57 MB | |

| 手册 - 开发工具 | PDF 693 KB | |

5 items

|

||

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件