概览

描述

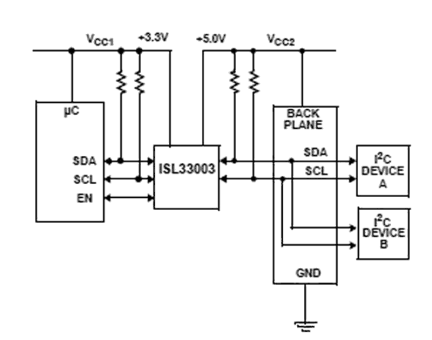

The ISL33001 two-channel bus buffer provides the buffering necessary to extend the bus capacitance beyond the 400pF maximum specified by the I2C specification. In addition, the ISL33001 features rise time accelerator circuitry to reduce power consumption from passive bus pull-up resistors and improve data-rate performance. The device also includes hot-swap circuitry to prevent corruption of the data and clock lines when I2C devices are plugged into a live backplane. The ISL33001 operates at supply voltages from +2.3V to +5.5V at a temperature range of -40 °C to +85 °C.

特性

- two-channel I2C compatible bidirectional buffer

- +2.3VDC to +5.5VDC supply range

- 400kHz operation

- Bus capacitance buffering

- Rise time accelerators

- Hot swapping capability

- ±6kV Class 3 HBM ESD protection on all pins

- ±12kV HBM ESD protection on SDA/SCL pins

- Enable pin

- READY logic pin

- Pb-free (RoHS Compliant) 8 Ld SOIC, 8 Ld TDFN (3mm x 3mm) and 8 Ld MSOP packages

- Low quiescent current: 2.1mA typ.

- Low shutdown current: 0.5µA typ.

产品对比

应用

设计和开发

开发板与套件

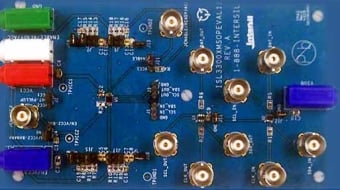

I2C Bus Buffer with Rise Time Accelerators and Hot Swap Capability Evaluation Board

The ISL33001MSOPEVAL1Z evaluation board is designed to provide a quick and easy method for evaluating the ISL33001 two-channel bus buffer with rise time accelerators and hot-swap capability.

Discrete NMOS transistors are used to produce the pull-down functions of a wired-AND bus. Each SDA/SCL pin...

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件