封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | QSOP |

| Pkg. Code: | MLN |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 8.6 x 3.9 x 0.00 |

| Pitch (mm): | 0.6 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| RoHS (ISL6754AAZA) | 下载 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | QSOP |

| Lead Count (#) | 20 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| Pb Free Category | Pb-Free 100% Matte Tin Plate w/Anneal-e3 |

| Temp. Range (°C) | -40 to +105°C |

| Control Mode | Peak Current Mode or Voltage Mode |

| Duty Cycle (%) | 99 - 99 |

| FET Driver Output Current (Max) (A) | 0.01 |

| Length (mm) | 8.6 |

| MOQ | 580 |

| No-Load Operating Current | 11 mA (typ), 15.5 mA (max) |

| PWMs (#) | 6 |

| Parametric Category | Zero Voltage Switching (ZVS) Full Bridge Controllers |

| Pitch (mm) | 0.6 |

| Pkg. Dimensions (mm) | 8.6 x 3.9 x 0.00 |

| Qualification Level | Standard |

| Switching Frequency (KHz) | 2000 - 2000 |

| Topology Characteristic | Full-Bridge ZVS |

| Topology [Rail 1] | Zero-Voltage-Switching (ZVS) |

| UVLO Falling (V) | 7 |

| UVLO Rising (V) | 8.75 |

| VBIAS (Max) (V) | 20 |

| Width (mm) | 3.9 |

有关 ISL6754 的资源

描述

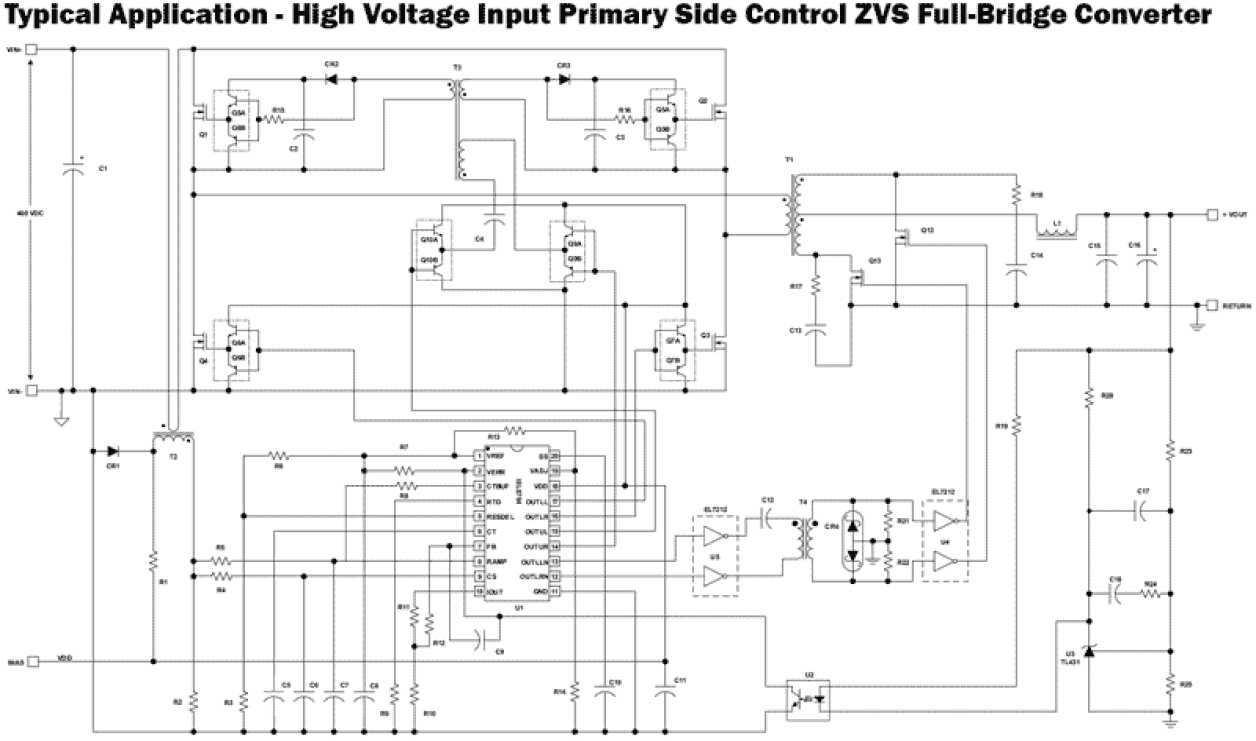

The ISL6754 is a high performance extension of the Renesas family of Zero-Voltage Switching (ZVS) full-bridge PWM controllers. Like the ISL6752, it achieves ZVS operation by driving the upper bridge FETs at a fixed 50% duty cycle while the lower bridge FETs are trailing-edge modulated with adjustable resonant switching delays. Adding to the ISL6752’s feature set are average current monitoring and soft-start. The average current signal may be used for average current limiting, current sharing circuits and average current mode control. Additionally, the ISL6754 supports both voltage- and current-mode control. The ISL6754 features complemented PWM outputs for Synchronous Rectifier (SR) control. The complemented outputs may be dynamically advanced or delayed relative to the PWM outputs using an external control voltage. This advanced BiCMOS design features precision dead time and resonant delay control, and an oscillator adjustable to 2MHz operating frequency. Additionally, multi-pulse suppression ensures alternating output pulses at low duty cycles where pulse skipping may occur.