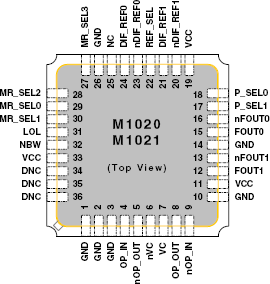

封装信息

| Lead Count (#) | 36 |

| Pkg. Type | CLCC |

| Pkg. Code | CG36 |

| Pitch (mm) | 0.6 |

| Pkg. Dimensions (mm) | 9.0 x 9.0 x 2.8 |

环境和出口类别

| Pb (Lead) Free | Yes |

| HTS (US) | 8542390000 |

| Moisture Sensitivity Level (MSL) | 1 |

| ECCN (US) |

产品属性

| Pkg. Type | CLCC |

| Lead Count (#) | 36 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tube |

| Abs. Pull Range Min. (± PPM) | 120 |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 15 - 700 |

| Input Type | LVCMOS, LVPECL, LVDS |

| Inputs (#) | 2 |

| Length (mm) | 9 |

| MOQ | 57 |

| Moisture Sensitivity Level (MSL) | 1 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 62.5 - 62.5, 125 - 125 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 2 |

| Package Area (mm²) | 81.0 |

| Pb Free Category | e4 Au |

| Phase Jitter Max RMS (ps) | 0.600 |

| Phase Jitter Typ RMS (ps) | 0.400 |

| Pitch (mm) | 0.6 |

| Pkg. Dimensions (mm) | 9.0 x 9.0 x 2.8 |

| Prog. Clock | No |

| Qty. per Carrier (#) | 54 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range | 0 to 70°C |

| Thickness (mm) | 2.8 |

| Width (mm) | 9 |

描述

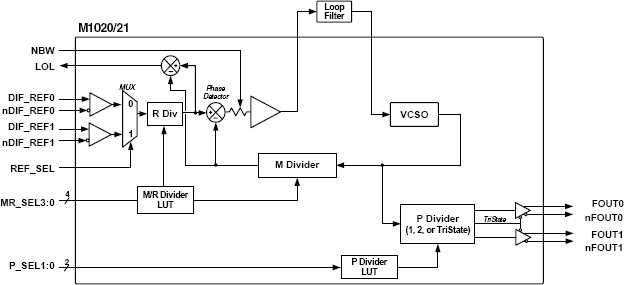

The M1020/21 is a VCSO (Voltage Controlled SAW Oscillator) based clock jitter attenuator PLL designed for clock jitter attenuation and frequency translation. The device is ideal for generating the transmit reference clock for optical network systems supporting up to 2.5Gb data rates. It can serve to jitter attenuate a stratum reference clock or a recovered clock in loop timing mode. The M1020/21 module includes a proprietary SAW (surface acoustic wave) delay line as part of the VCSO. This results in a high frequency, high-Q, low phase noise oscillator that assures low intrinsic output jitter.