特性

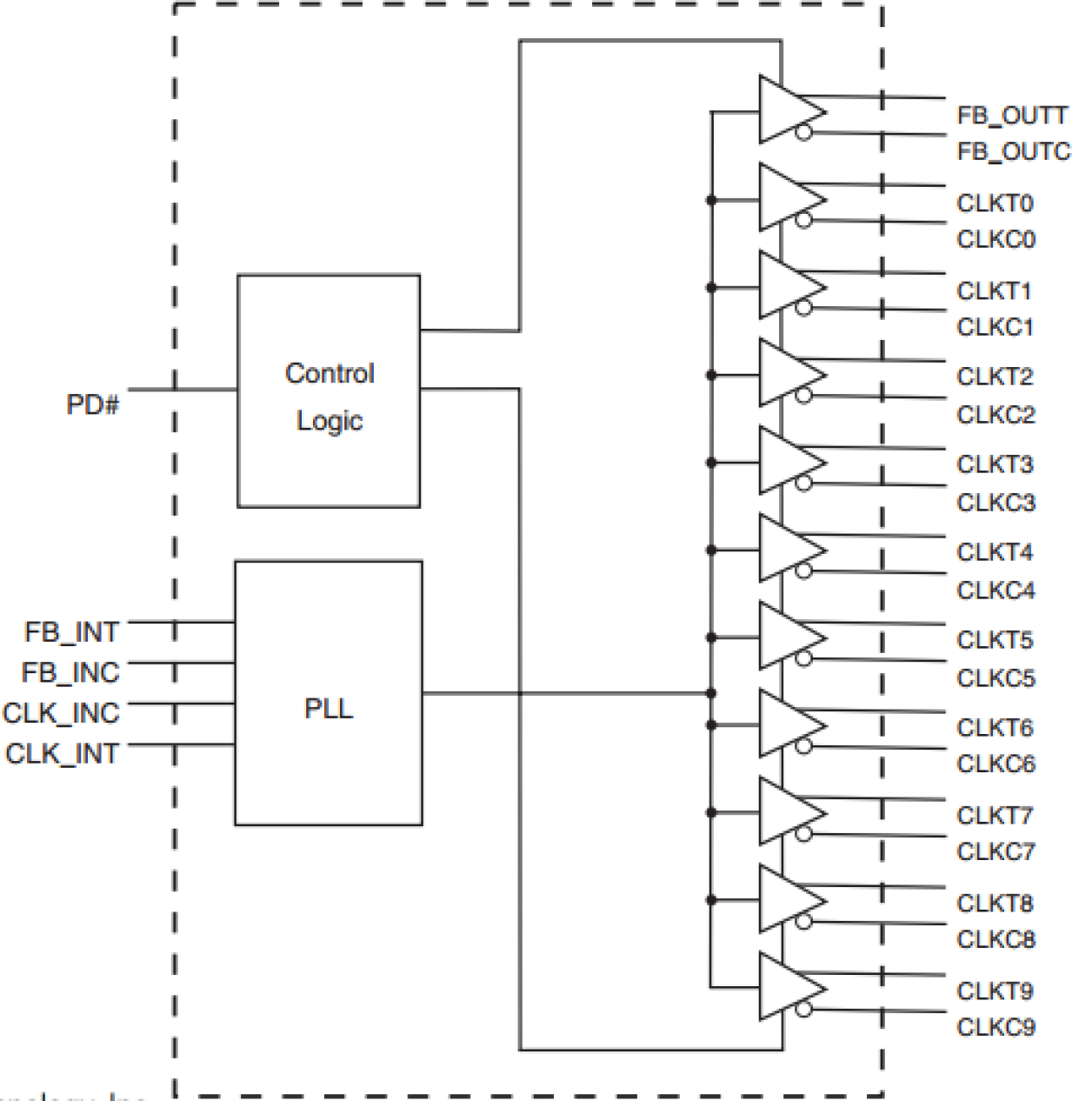

- Low skew, low jitter PLL clock driver

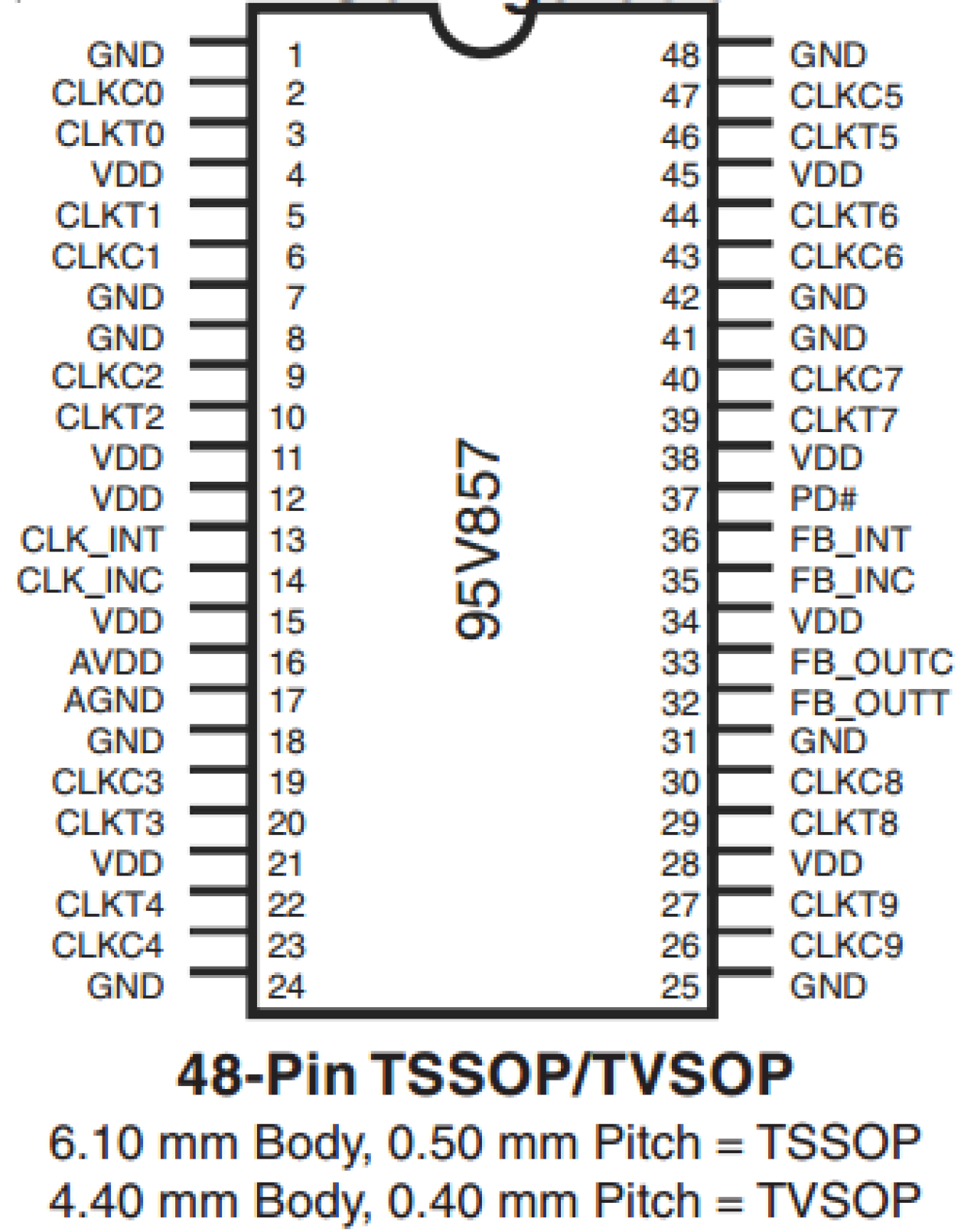

- 1 to 10 differential clock distribution (SSTL_2)

- Feedback pins for input to output synchronization

- PD# for power management

- Spread Spectrum-tolerant inputs

- Auto PD when input signal removed

- Choice of static phase offset available, for easy board tuning

描述

2.5V Wide Range Frequency DDR1 Clock Driver (45MHz - 233MHz)

当前筛选条件