概览

描述

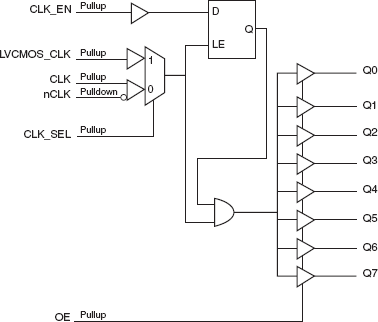

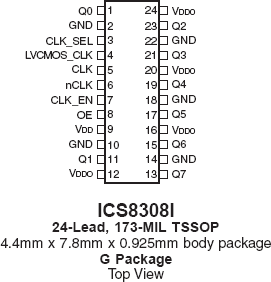

The 8308I is a low-skew, 1-to-8 Fanout Buffer. The 8308I has two selectable clock inputs. The CLK, nCLK pair can accept most differential input levels. The LVCMOS_CLK can accept LVCMOS or LVTTL input levels. The low impedance LVCMOS/ LVTTL outputs are designed to drive 50? series or parallel terminated transmission lines. The effective fanout can be increased from 8 to 16 by utilizing the ability of the outputs to drive two series terminated transmission lines. The 8308I is characterized for 3.3V core/3.3V output, 3.3V core/2.5V output or 2.5V core/2.5V output operation. Guaranteed output and part-part skew characteristics make the 8308I ideal for those clock distribution applications requiring well defined performance and repeatability.

特性

- Eight LVCMOS/LVTTL outputs, (7Ω typical output impedance)

- Selectable LVCMOS_CLK or differential CLK, nCLK inputs

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- Maximum Output Frequency: 350MHz

- Output Skew: (3.3V± 5%): 100ps (maximum)

- Part to Part Skew: (3.3V± 5%): 1ns (maximum)

- Supply Voltage Modes: (Core/Output) 3.3V/3.3V 3.3V/2.5V 2.5V/2.5V

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

产品对比

应用

设计和开发

产品选项

当前筛选条件