- Achieves flexible, small-block configuration for large-scale TCAMs

- Cuts search energy and boosts speed through efficient search processing

- Enhanced functional safety enables application beyond networking to automotive SoCs

- New technology presented at ISSCC 2026 in San Francisco

TOKYO, Japan and SAN FRANCISCO, Calif. ― Renesas Electronics Corporation (TSE:6723), a premier supplier of advanced semiconductor solutions, today announced a configurable ternary content-addressable memory (TCAM) built on a 3nm FinFET process. The new TCAM simultaneously delivers higher density, lower power and strengthened functional safety, making it suitable for automotive applications. Renesas presented the results at the International Solid-State Circuits Conference 2026 (ISSCC 2026), held February 15–19 in San Francisco, USA.

With the rapid expansion of 5G and cloud/edge computing, network traffic continues to surge, driving demand for large and diverse TCAM configurations such as 256-bit × 4,096 entries. Conventional scaling that relies solely on hard macros increases peripheral area due to more banks and repeaters and makes timing closure more difficult, while also raising search power. Automotive applications further require higher safety coverage to meet standards such as ISO 26262. Renesas addresses these challenges with the following innovations.

1. Integrated Hard- and Soft-Macro Approach for Flexible Configuration

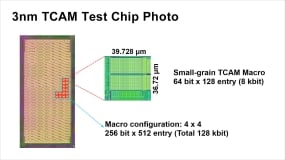

The newly developed TCAM hard macros are supported by a memory compiler in fine granularities—search key widths of 8–64 bits and entry depths of 32–128. Larger configurations (e.g., 256-bit × 4,096 entries) are realized by combining these hard macros with tool-driven soft-macro auto-generation to provide a configurable single macro that covers a wide range of use cases on one chip. This achieves an industry-leading memory density of 5.27 Mb/mm².

2. All-mismatch Detection and Macro-Level Pipelined Search

Each hard macro integrates an all-mismatch detection circuit (Note 1) and executes a two-stage pipelined search. Based on the first-stage result, the second stage can be continued or halted to avoid unnecessary energy consumption. For example, in 64–256-bit × 512-entry configurations, the approach reduces search energy by:

- Up to 71.1% with column-wise pipelined search (with key partitioning, >64-bit keys)

- Up to 65.3% with row-wise pipelined search (without key partitioning, ≤64-bit keys)

In a 256-bit × 512-entry configuration, the design achieves low-power operation with search energy of 0.167 fJ/bit, and the distributed timing load enables a 1.7 GHz search clock. The resulting TCAM figure-of-merit (density × speed ÷ energy) reaches 53.8, exceeding prior work.

3. Enhanced Functional Safety for Automotive Applications (Split Data Bus and Dedicated SRAM)

Because TCAM bitcells for the same address are physically adjacent, a double-bit error caused by soft errors cannot be corrected by conventional SECDED ECC (Note 2). Renesas mitigates this with two techniques:

- Split odd/even data buses for user data and ECC parity to increase physical separation between memory cells, converting potential double-bit errors into correctable single-bit errors.

- Dedicated SRAM for ECC parity with an address decoder independent of the TCAM, improving detectability when an incorrect address is selected during TCAM writes.

These measures significantly improve safety coverage required in automotive contexts. The TCAM’s flexible key widths and entry depths, combined with power savings and robust functional safety, make it well-suited not only for automotive use but also for industrial and consumer devices where high-speed data exchange between sensors and processors is essential. Renesas will continue to advance memory architectures that deliver high capacity, low power and high reliability.

Notes

- All-mismatch detection: A circuit that determines in the first search stage whether all entries are mismatches and controls whether the second stage is executed.

- SECDED (Single Error Correction, Double Error Detection): An ECC scheme that corrects single-bit errors and detects double-bit errors.

About Renesas Electronics Corporation

Renesas Electronics Corporation (TSE: 6723) empowers a safer, smarter and more sustainable future where technology helps make our lives easier. A leading global provider of microcontrollers, Renesas combines our expertise in embedded processing, analog, power and connectivity to deliver complete semiconductor solutions. These Winning Combinations accelerate time to market for automotive, industrial, infrastructure and IoT applications, enabling billions of connected, intelligent devices that enhance the way people work and live. Learn more at renesas.com. Follow us on LinkedIn, Facebook, X, YouTube, and Instagram.

(Remarks). All names of products or services mentioned in this press release are trademarks or registered trademarks of their respective owners.

The content in the press release, including, but not limited to, product prices and specifications, is based on the information as of the date indicated on the document, but may be subject to change without prior notice.