特性

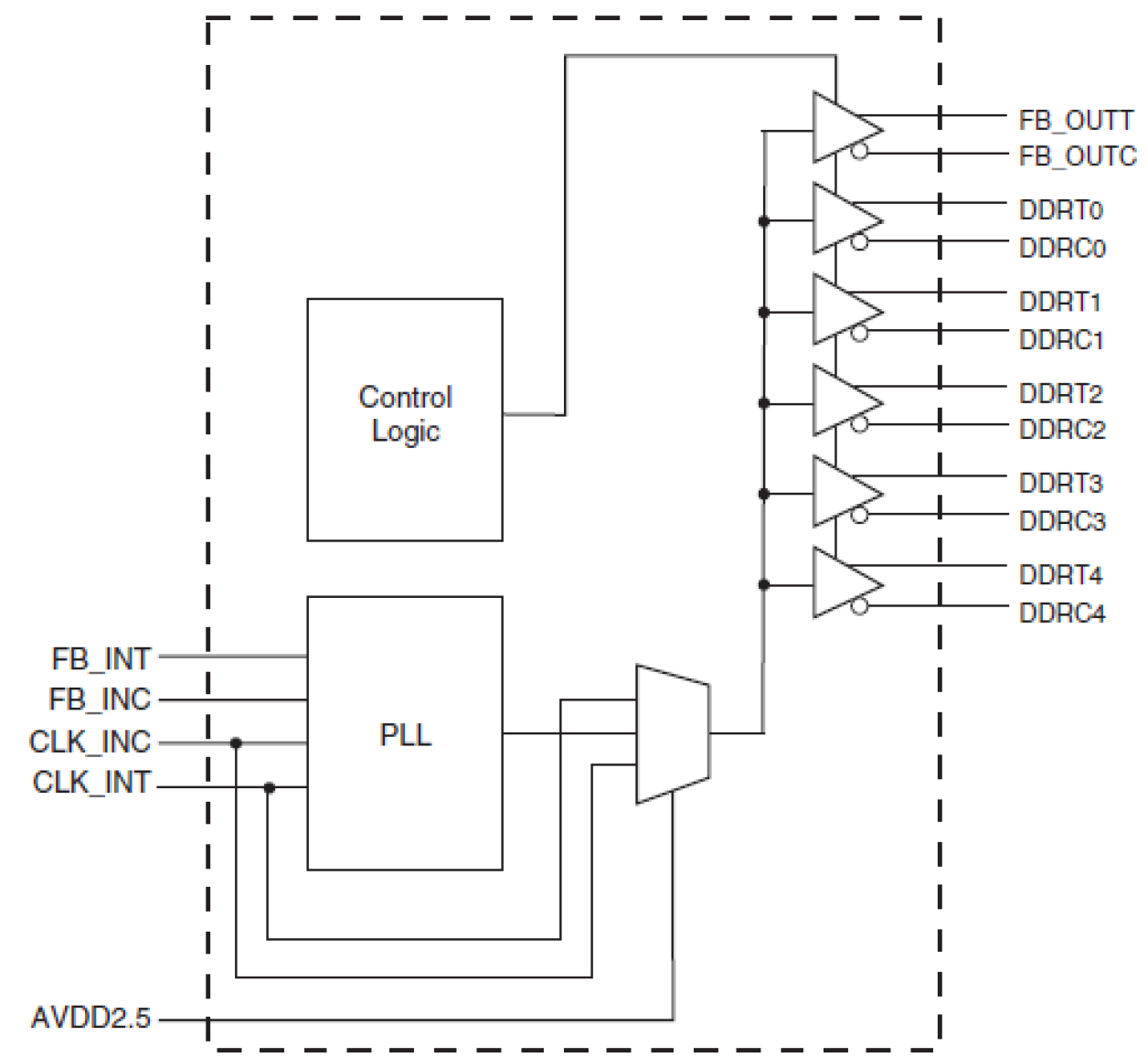

- Low skew, low jitter PLL clock driver

- External feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs with bypass mode mux

- Operating frequency: 60 to 170 MHz

- Operating Temperature: -45°C to +85°C

- Cycle - Cycle jitter: <75ps

- Output - Output skew: <60ps

- Output Rise and Fall Time: 650ps - 950ps

描述

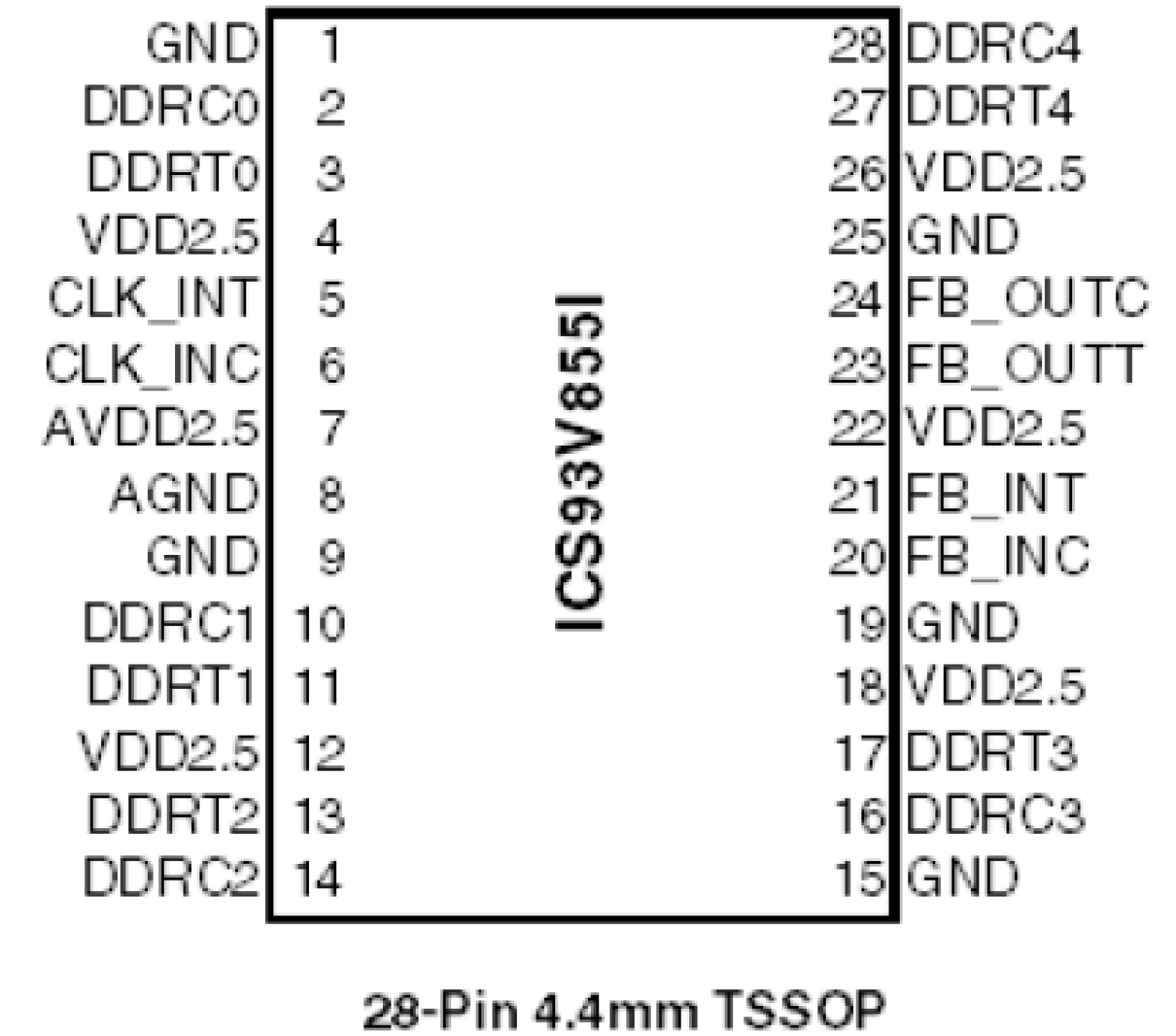

2.5V 1 to 4 differential clock distributor. Optimized for clock distribution in DDR SDRAM applications. Operating frequency: 60MHZ to 220MHz

当前筛选条件

加载中