特性

- High voltage type (20V rating)

- Medium-speed operation tPHL, tPLH = 65ns (typ) at VDD = 10V, CL = 50pF

- 100% tested for quiescent current at 20V

- Standardized symmetrical output characteristics

- 5V, 10V and 15V parametric ratings

- Maximum input current of 1µA at 18V over full package temperature range; 100nA at 18V and +25 °C

- Noise margin (over full package temperature range): 1V at VDD = 5V, 2V at VDD = 10V, 2.5V at VDD = 15V

- Meets all requirements of JEDEC tentative standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

描述

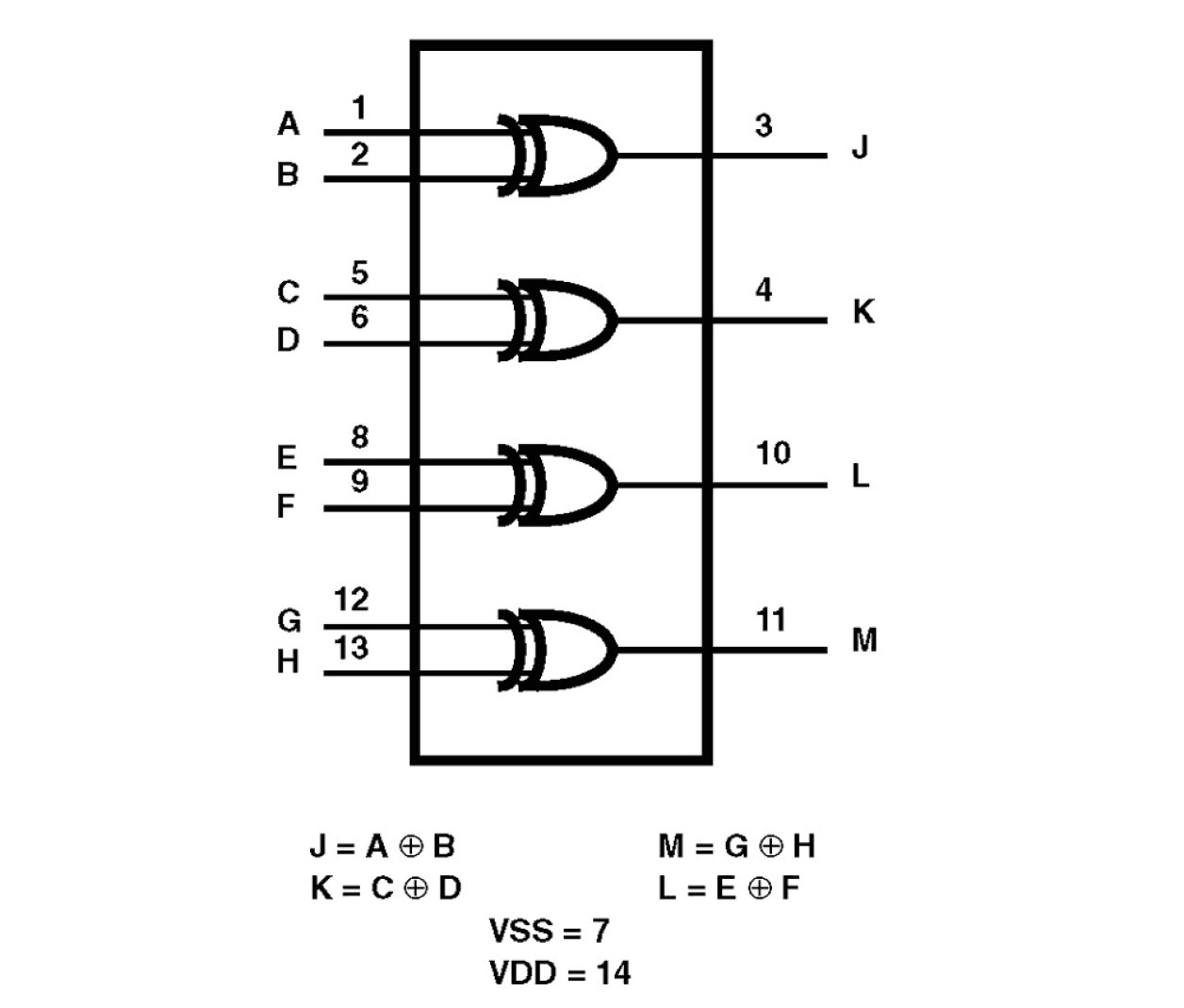

The CD4030BMS types consist of four independent Exclusive OR gates. The CD4030BMS provides the system designer with a means for the direct implementation of the Exclusive OR function. The CD4030BMS is supplied in these 14-lead outline packages: Braze Seal DIP H4H, Frit Seal DIP H1B, Ceramic Flatpack H3W.

应用

- Even and odd-parity generators and checkers

- Logical comparators

- Adders/Subtractors

- General logic functions

当前筛选条件

加载中