特性

- Quad 16-bit DAC, up to 2.0Gsps output update rate

- Up to 1Gsps baseband input data rate with x2, x4, and x8 interpolation

- Configurable JESD204B serial input lanes at up to 10Gbps

- JEDEC JESD204B device subclass 0 and 1 compliant, Xilinx LogiCORE IP

- Multiple-device synchronization (MDS) capable

- Input clock divider (2, 4, 6, 8) with group delay compensation

- RF enable/disable pin and RF automatic mute for PA protection

- Integrated low-noise bypassable PLL

- Two embedded NCOs with 40-bit programmable frequency

- Two embedded embedded complex (IQ) digital modulators

- Power consumption 400mW per channel at 1.5Gsps

- Output common mode voltage 3.0V typical

- Typ. performance: SFDR = 85dBc, IMD3 = 85dBc, NSD = -164dBm/Hz

- Xilinx LogiCORE IP JESD204

- See: Altera JESD204B Reference Designs

描述

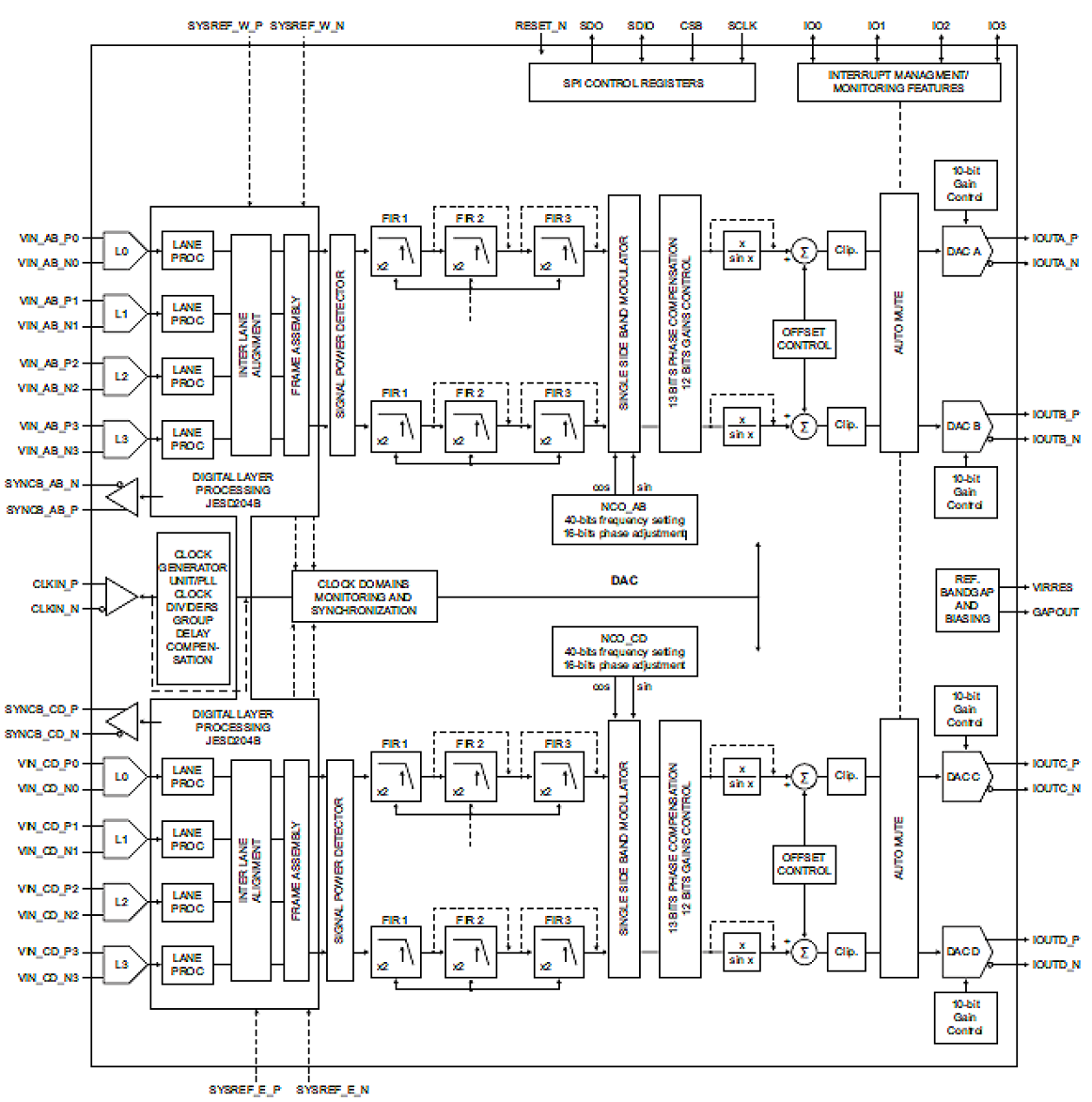

The DAC1658Q is a high-speed, high-performance 16-bit quad-channel digital-to-analog converter (DAC). The device provides sample rates up to 2.0Gsps with selectable 2x, 4x, and 8x interpolation filters optimized for multi-carrier and broadband wireless transmitters. The DAC1658Q integrates a JEDEC JESD204B-compliant high-speed serial input data interface running up to 10Gbps allowing dual channel input sampling at up to 1Gsps over four differential lanes. It offers numerous advantages over traditional parallel digital interfaces. The DAC1658Q integrates a very low noise bypassable phase-locked loop (PLL), two embedded NCOs with 40-bit programmable frequency, and two embedded complex (IQ) digital modulators. It is configured with high output common mode from 2.8V to 3.0V.

当前筛选条件