概览

描述

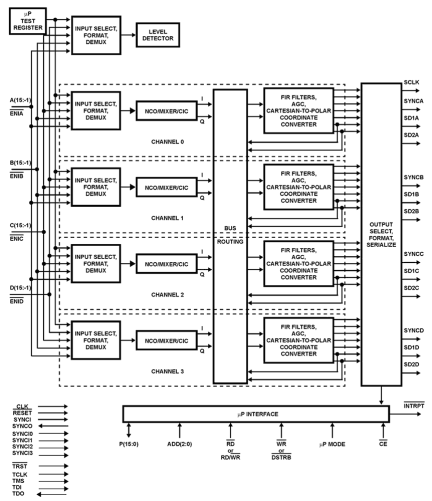

The ISL5216 Quad Programmable Digital Downconverter (QPDC) is designed for high dynamic range applications such as cellular basestations where multiple channel processing is required in a small physical space. The QPDC combines into a single package a set of four channels which include: digital mixers, a quadrature carrier NCO, digital filters, a resampling filter, a cartesian to polar coordinate converter, and an automatic gain control (AGC) loop. The ISL5216 accepts four channels of 16-bit fixed or up to 14-bit mantissa/3-bit exponent floating point real or complex digitized IF samples which are mixed with local quadrature sinusoids. Each channel carrier NCO frequency is set independently by the microprocessor. The output of the mixers is filtered with CIC and FIR filters, with a variety of decimation options. Gain adjustment is provided on the filtered signal. The digital AGC provides a gain adjust range of up to 96dB with programmable thresholds and slew rates. A cartesian to polar coordinate converter provides magnitude and phase outputs. A frequency discriminator is also provided to allow FM demodulation. Selectable outputs include I samples, Q samples, magnitude, phase, frequency, and AGC gain. The output resolution is selectable from a 4-bit fixed point to a 32-bit floating point. Output bandwidths in excess of 1MHz are achievable using a single channel. Wider bandwidths are available by cascading or polyphasing multiple channels.

特性

- Up to 95MSPS input

- Four independently programmable downconverter channels in a single package

- Four parallel 17-bit inputs providing 16-bit fixed or one of several 17-bit floating point formats

- 32-bit programmable carrier NCO with >115dB SFDR

- 110dB FIR out of band attenuation

- Decimation from 4 to >65536

- 24-bit internal data path

- Digital AGC with up to 96dB of gain range

- Filter functions

- 1- to 5-stage CIC filter

- Halfband decimation and interpolation FIR filtering

- Programmable FIR filtering

- Resampling FIR filtering

- Cascadable filtering for additional bandwidth

- Four independent serial outputs

- 2.5V core, 3.3V I/O operation

- Pb-free plus anneal available (RoHS compliant)

产品对比

应用

文档

|

|

|

|

|---|---|---|

| 类型 | 文档标题 | 日期 |

| 数据手册 | PDF 2.84 MB | |

| EOL 通告 | PDF 1.17 MB | |

| 应用说明 | PDF 360 KB | |

| 应用说明 | PDF 427 KB | |

| 应用说明 | PDF 541 KB | |

5 items

|

||

设计和开发

软件与工具

开发板与套件

Four-Channel Programmable Digital Downconverter Evaluation Board

The ISL5216EVAL1 evaluation board is used to evaluate the ISL5216 four-channel programmable digital downconverter.

The ISL5216 quad programmable digital downconverter (QPDC) is designed for high dynamic range applications such as cellular basestations where multiple channel processing is...

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件