封装信息

| CAD 模型: | View CAD Model |

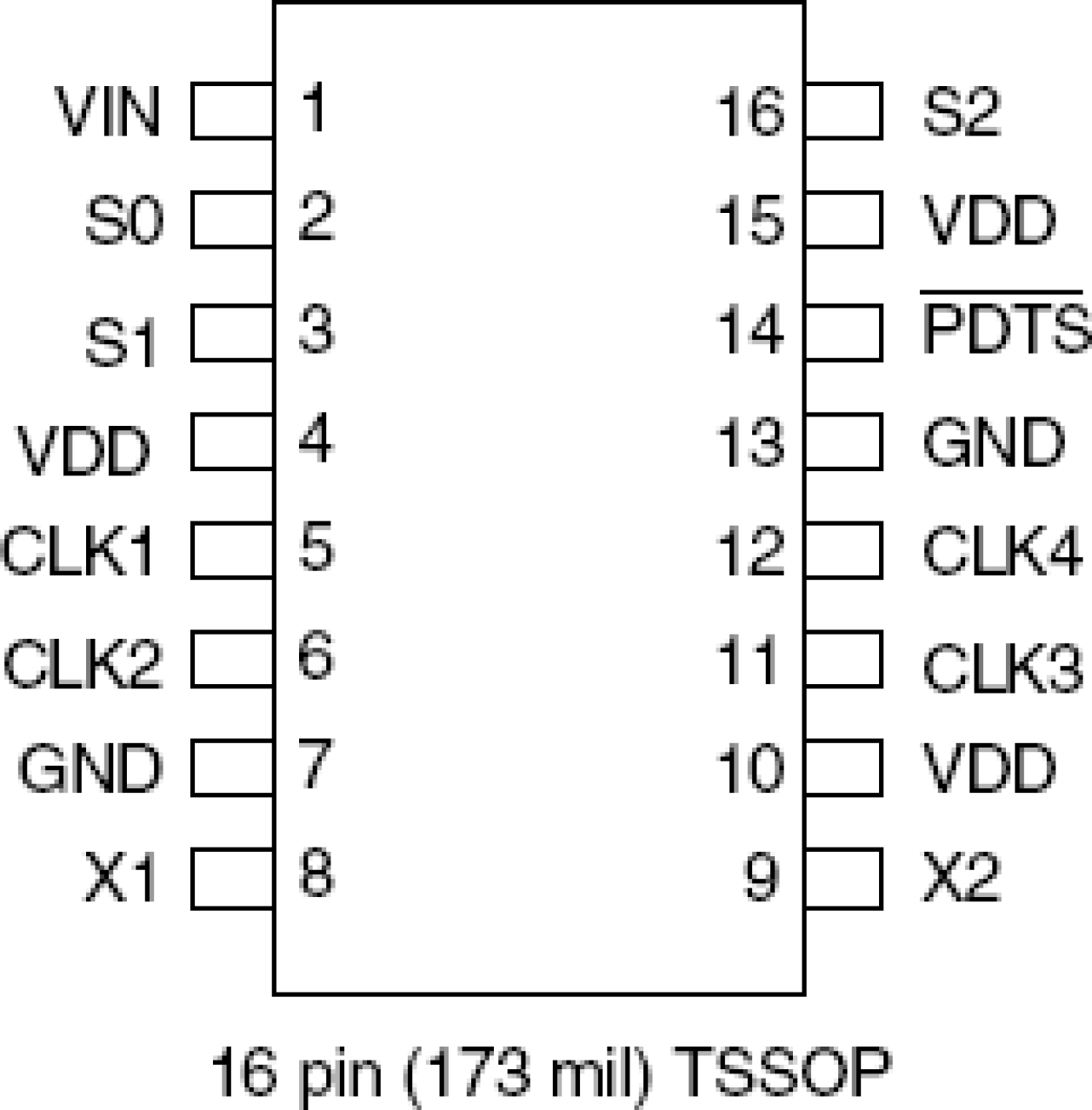

| Pkg. Type: | TSSOP |

| Pkg. Code: | PGG16 |

| Lead Count (#): | 16 |

| Pkg. Dimensions (mm): | 5.0 x 4.4 x 1.0 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

| Moisture Sensitivity Level (MSL) | 1 |

产品属性

| Pkg. Type | TSSOP |

| Lead Count (#) | 16 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tube |

| Advanced Features | Programmable Clock, Reference Output |

| Core Voltage (V) | 3.3 |

| Family Name | VersaClock |

| Input Freq (MHz) | 27 |

| Input Type | Crystal |

| Inputs (#) | 1 |

| Length (mm) | 5 |

| MOQ | 144 |

| Moisture Sensitivity Level (MSL) | 1 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 200 |

| Output Skew (ps) | 250 |

| Output Type | LVCMOS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 4 |

| Package Area (mm²) | 22 |

| Pb Free Category | e3 Sn |

| Period Jitter Typ P-P (ps) | 200 |

| Phase Jitter Typ RMS (fs) | 50000 |

| Phase Jitter Typ RMS (ps) | 50 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 5.0 x 4.4 x 1.0 |

| Prog. Clock | Yes |

| Prog. Interface | OTP |

| Qty. per Carrier (#) | 96 |

| Qty. per Reel (#) | 0 |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | No |

| Temp. Range (°C) | -40 to 85°C |

| Thickness (mm) | 1 |

| Width (mm) | 4.4 |

有关 275 的资源

描述

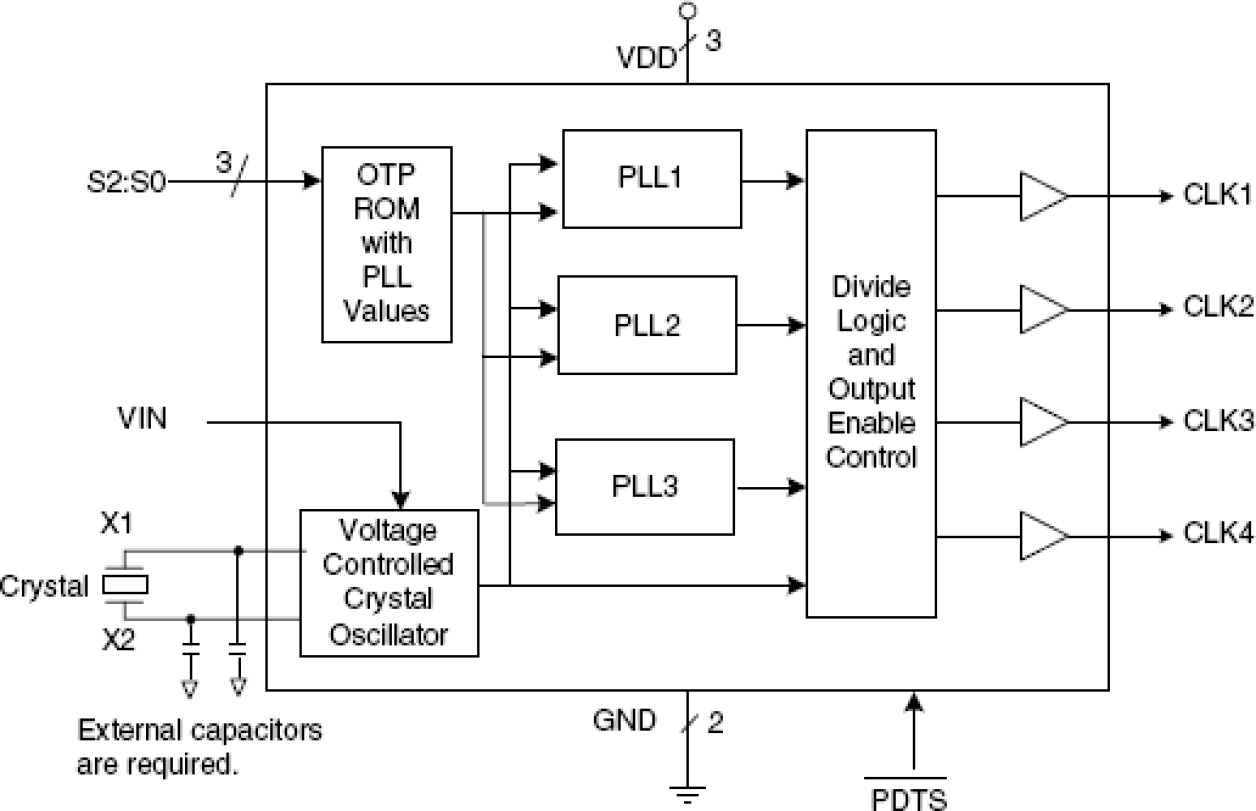

The 275 field programmable VCXO clock synthesizer generates up to four high-quality, high-frequency clock outputs including multiple reference clocks from a low-frequency crystal input. It is designed to replace crystals and crystal oscillators in most electronic systems. Using IDT's VersaClockTM software to configure PLLs and outputs, the 275 contains a One-Time Programmable (OTP) ROM for field programmability. Programming features include VCXO, eight selectable configuration registers and up to two sets of two low-skew outputs. Using Phase-Locked Loop (PLL) techniques, the device runs from a standard fundamental mode, inexpensive crystal, or clock. It can replace VCXOs, multiple crystals and oscillators, saving board space and cost. The 275 is also available in factory programmed custom versions for high-volume applications.