封装信息

| CAD 模型: | View CAD Model |

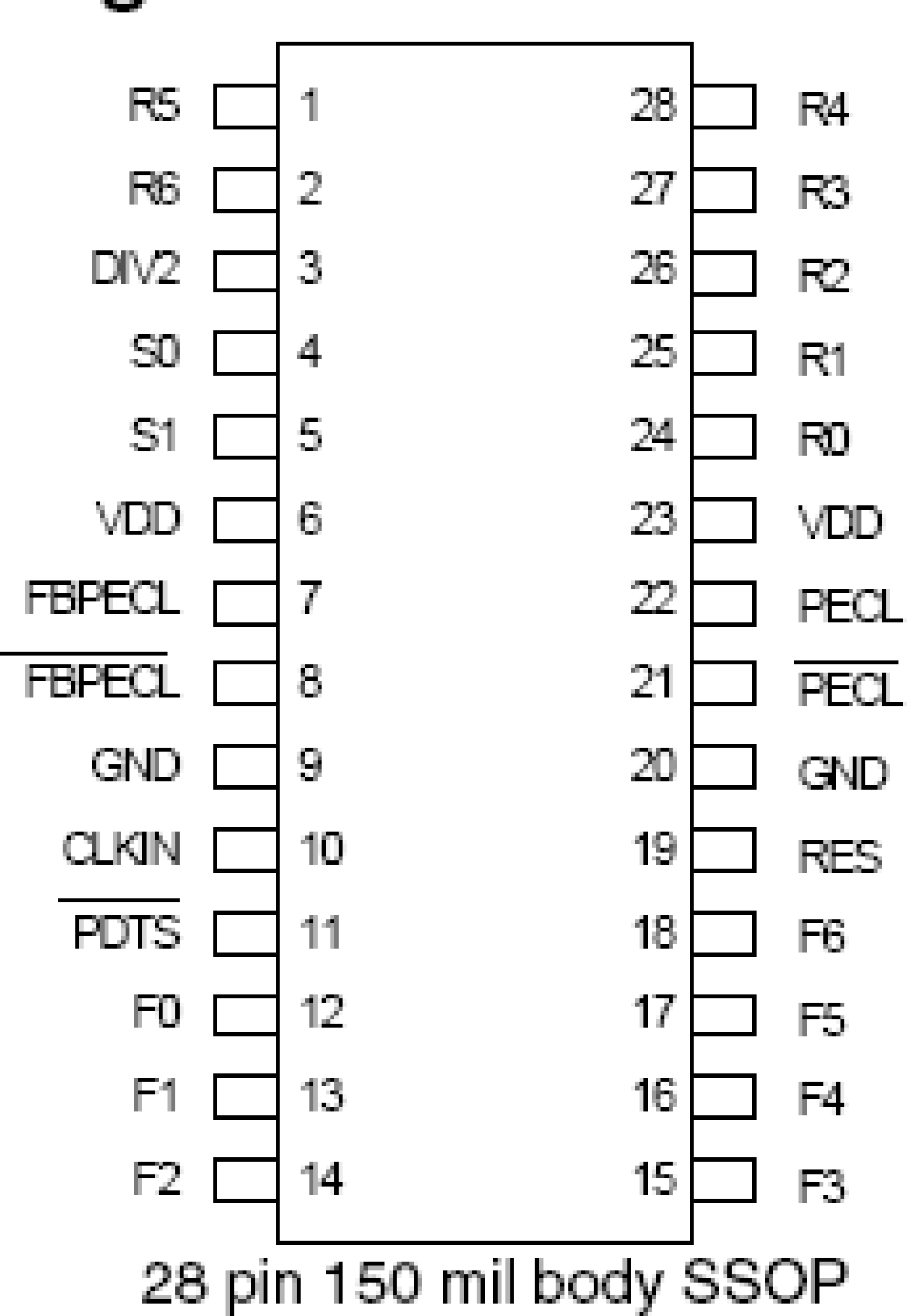

| Pkg. Type: | QSOP |

| Pkg. Code: | PCG28 |

| Lead Count (#): | 28 |

| Pkg. Dimensions (mm): | 9.9 x 3.8 x 1.47 |

| Pitch (mm): | 0.64 |

环境和出口类别

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

| Moisture Sensitivity Level (MSL) | 1 |

产品属性

| Pkg. Type | QSOP |

| Lead Count (#) | 28 |

| Pb (Lead) Free | Yes |

| Carrier Type | Reel |

| Advanced Features | Feedback Input |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Freq (MHz) | 1.5 - 200 |

| Input Type | LVCMOS |

| Inputs (#) | 1 |

| Length (mm) | 9.9 |

| MOQ | 2500 |

| Moisture Sensitivity Level (MSL) | 1 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 2.5 - 160 |

| Output Skew (ps) | 250 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 1 |

| Package Area (mm²) | 37.6 |

| Pb Free Category | e3 Sn |

| Period Jitter Typ P-P (ps) | 90 |

| Pitch (mm) | 0.64 |

| Pkg. Dimensions (mm) | 9.9 x 3.8 x 1.47 |

| Prog. Clock | No |

| Qty. per Carrier (#) | 0 |

| Qty. per Reel (#) | 2500 |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.47 |

| Width (mm) | 3.8 |

| 已发布 | No |

有关 527-03 的资源

描述

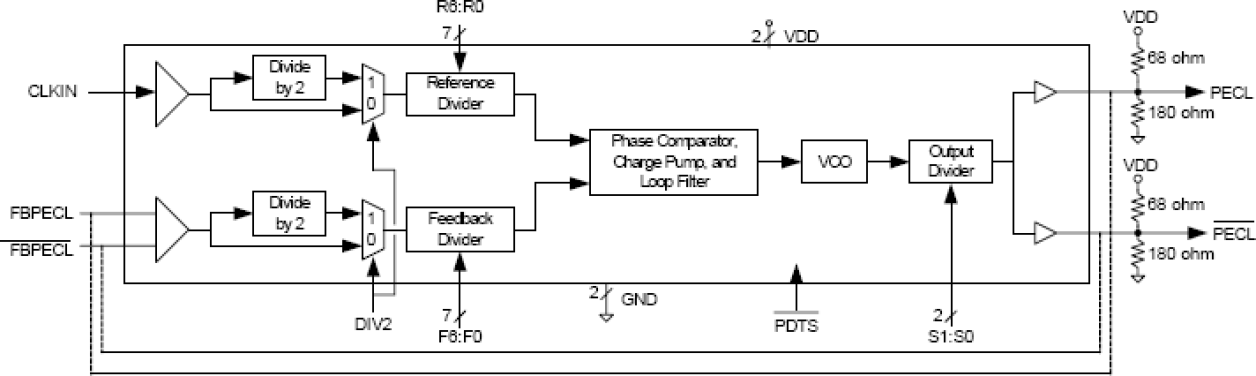

The 527-03 is the most flexible way to generate an output clock from an input clock with zero skew. The user can easily configure the device to produce nearly any output clock that is multiplied or divided from the input clock. The part supports non-integer multiplications and divisions. Using Phase-Locked Loop (PLL) techniques, the device accepts an input clock up to 200 MHz and produces an output clock up to 160 MHz. The 527-03 aligns rising edges on CLKIN with FBPECL at a ratio determined by the reference and feedback dividers. For a PECL input and output clock with zero delay, use the 527-04.