特性

- 16-pin TSSOP and VFQFPN packages; small board footprint

- Outputs can be terminated to LVDS; can drive a wider variety of devices

- OE control pin; greater system power management

- Industrial temperature range available; supports demanding embedded applications

- Cycle-to-cycle jitter: 80ps

- Output-to-output skew <50 ps

- PCIe Gen2 phase jitter <3.0ps RMS

- Low phase noise: 12kHz to 20MHz <6ps

- For PCIe Gen3 applications, see the IDT5V41315

描述

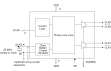

The IDT5V41285 is a PCIe Gen2 compliant clock generator. The device has 2 differential HCSL outputs. The output frequency is selectable via select pins.

当前筛选条件