特性

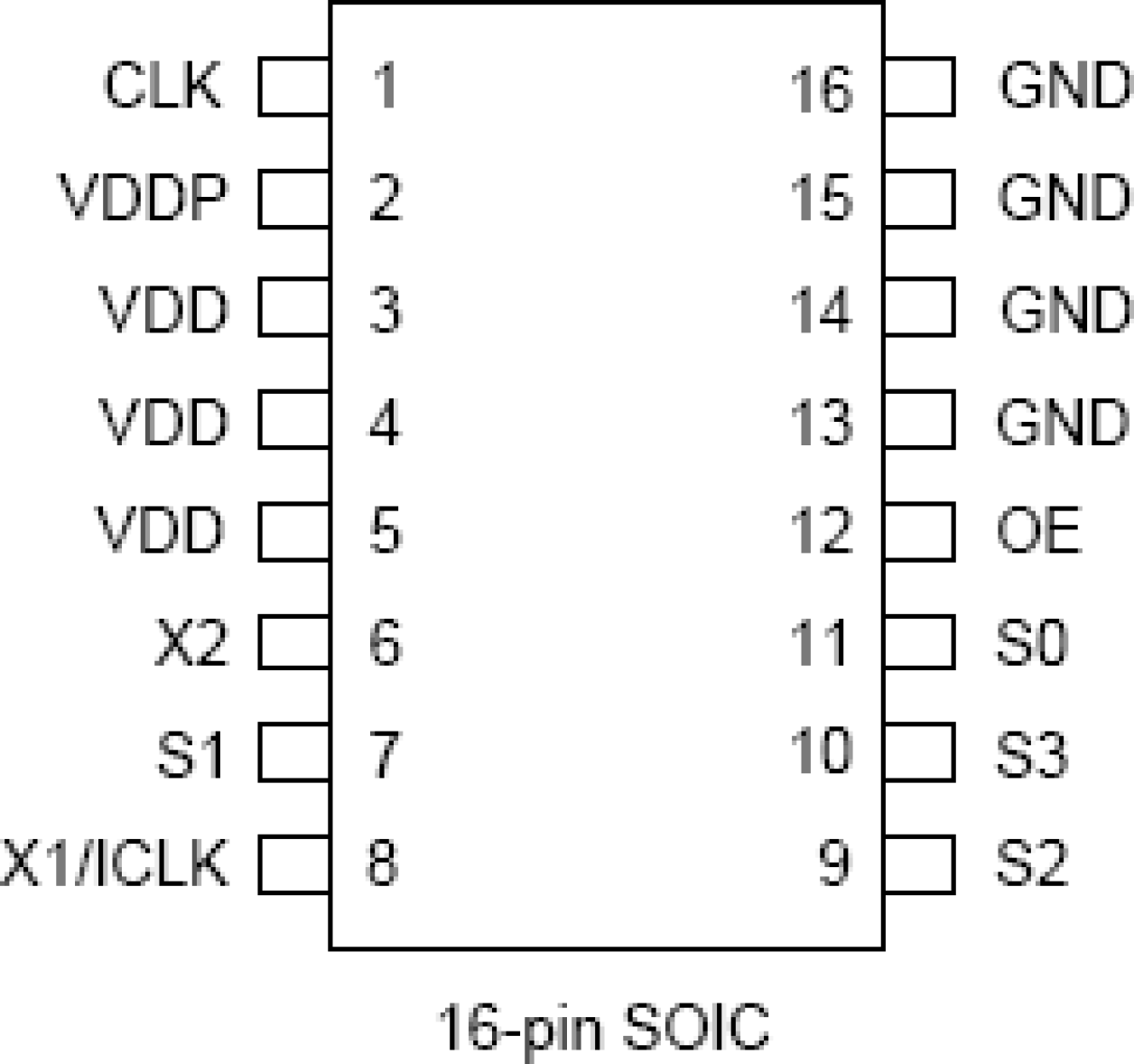

- Packaged in 16-pin SOIC (Pb free)

- Uses fundamental 10 - 27 MHz crystal or clock

- Patented PLL with the lowest phase noise

- Output clocks up to 170 MHz at 3.3 V

- Output Enable function tri-states outputs

- Low phase noise: -132 dBc/Hz at 10 kHz

- Low jitter - 18 ps one sigma

- Full swing CMOS outputs with 25 mA drive capability at TTL levels

- Advanced, low power, sub-micron CMOS process

- Industrial temperature range (-40 to +85°C)

- 3.3 V or 5 V core VDD. Output clock can operate down to 2.5 V

描述

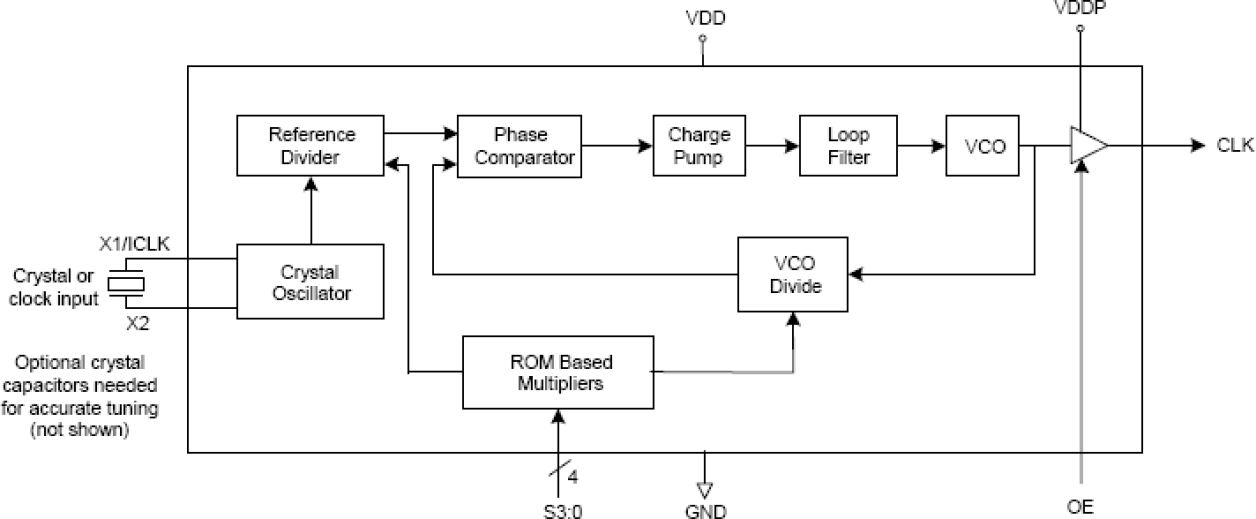

The 601-02 is a low cost, low phase noise, high performance clock synthesizer for any application that requires low phase noise and low jitter. The 601 is IDT's lowest phase noise multiplier. Using IDT's patented analog and digital Phase Locked Loop (PLL) techniques, the chip accepts a 10–27 MHz crystal or clock input, and produces output clocks up to 170 MHz at 3.3 V. A separate supply pin is provided so that the output can be 2.5 V. This product is intended for clock generation. It has low output jitter (variation in the output period), but input to output skew and jitter are not defined nor guaranteed. For applications which require defined input to output timing, use the 670-01.

当前筛选条件