特性

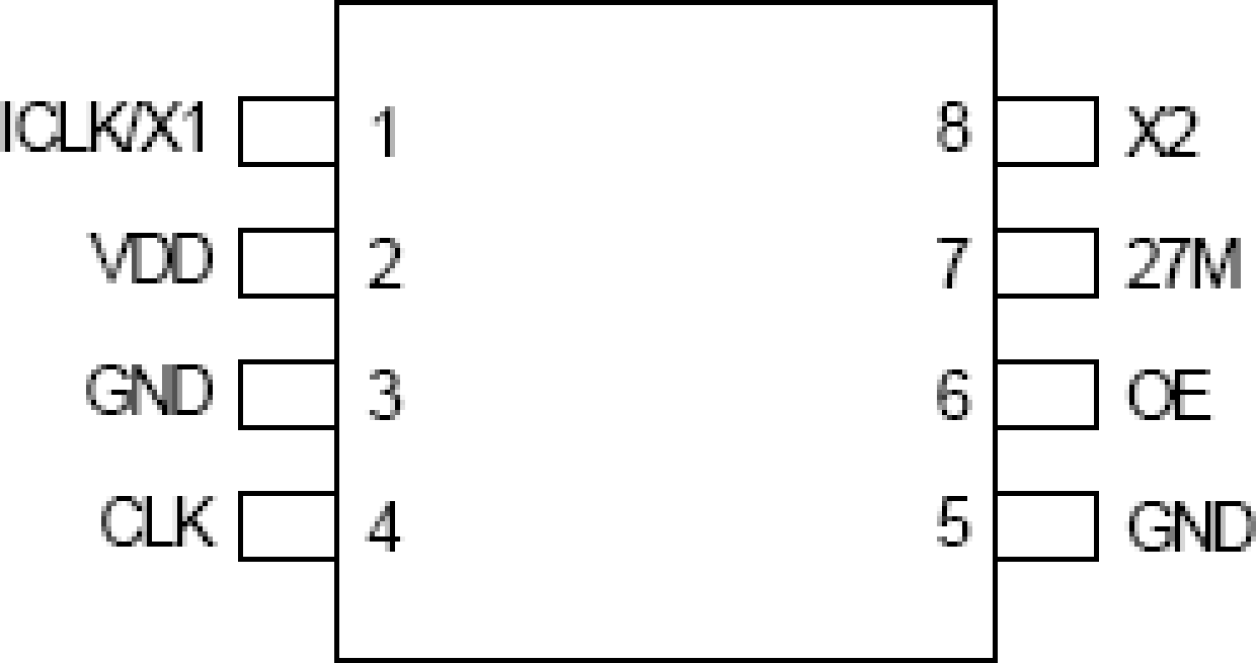

- Packaged in 8-pin SOIC

- Pb (lead) free package, RoHS compliant

- Input frequency of 27 MHz

- Zero ppm synthesis error in output clock

- 3.3 V ±5% operating supply

- Ideal for HDTV applications and oscillator manufacturers

- Advanced, low power, sub-micron CMOS process

描述

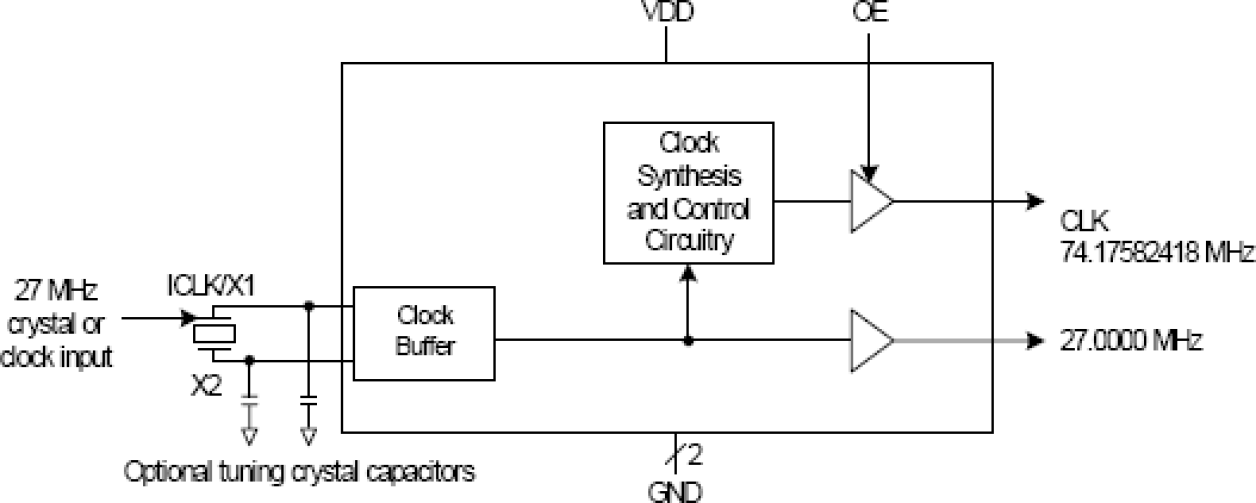

The 667-01 is a low-cost, low jitter, high-performance PLL clock synthesizer designed to produce the 74.176 MHz clock necessary for HDTV systems. Using IDT's patented analog Phase-Locked Loop (PLL) techniques, the device accepts a 27 MHz crystal or clock input. The zero ppm synthesis error exactly locks the display to the digital stream. IDT manufactures the largest variety multimedia clock synthesizers for all applications. Consult IDT to eliminate crystals and oscillators from your board.

当前筛选条件