特性

- 10 ns read/write cycle time

- Read and Write Clocks can be independent

- Dual-Ported zero fall-through time architecture

- Empty and Full Flags signal FIFO status

- Programmable Almost-Empty and Almost-Full flags can be set to any depth

- Programmable Almost-Empty and Almost-Full flags default to Empty+7, and Full-7, respectively

- Output enable puts output data bus in high-impedance state

- Available in 32-pin PLCC and 32-pin TQFP packages

- Industrial temperature range (–40C to +85C) is available

描述

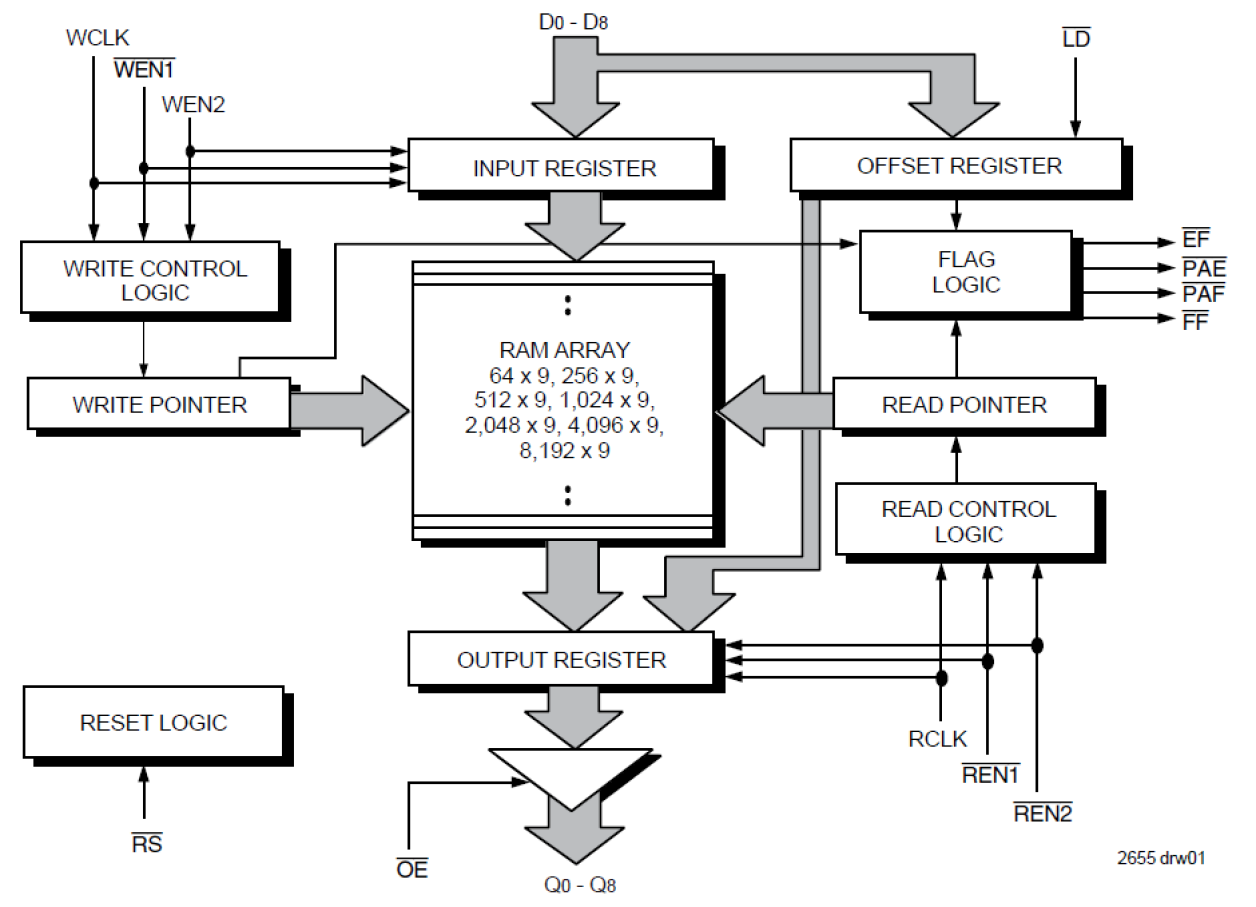

The 72221SyncFIFO™ is a 1K x 9 First-In, First-Out memory with clocked read and write controls. This FIFO is useful for a wide variety of data buffering needs such as graphics, local area networks and interprocessor communication. These FIFOs have 9-bit input and output ports. The Read Clock can be tied to the Write Clock for single clock operation or the two clocks can run asynchronous of one another for dual-clock operation.

当前筛选条件