封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | PK128 |

| Lead Count (#): | 128 |

| Pkg. Dimensions (mm): | 20.0 x 14.0 x 1.4 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Pb (Lead) Free | No |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Lead Count (#) | 128 |

| Pb (Lead) Free | No |

| Carrier Type | Reel |

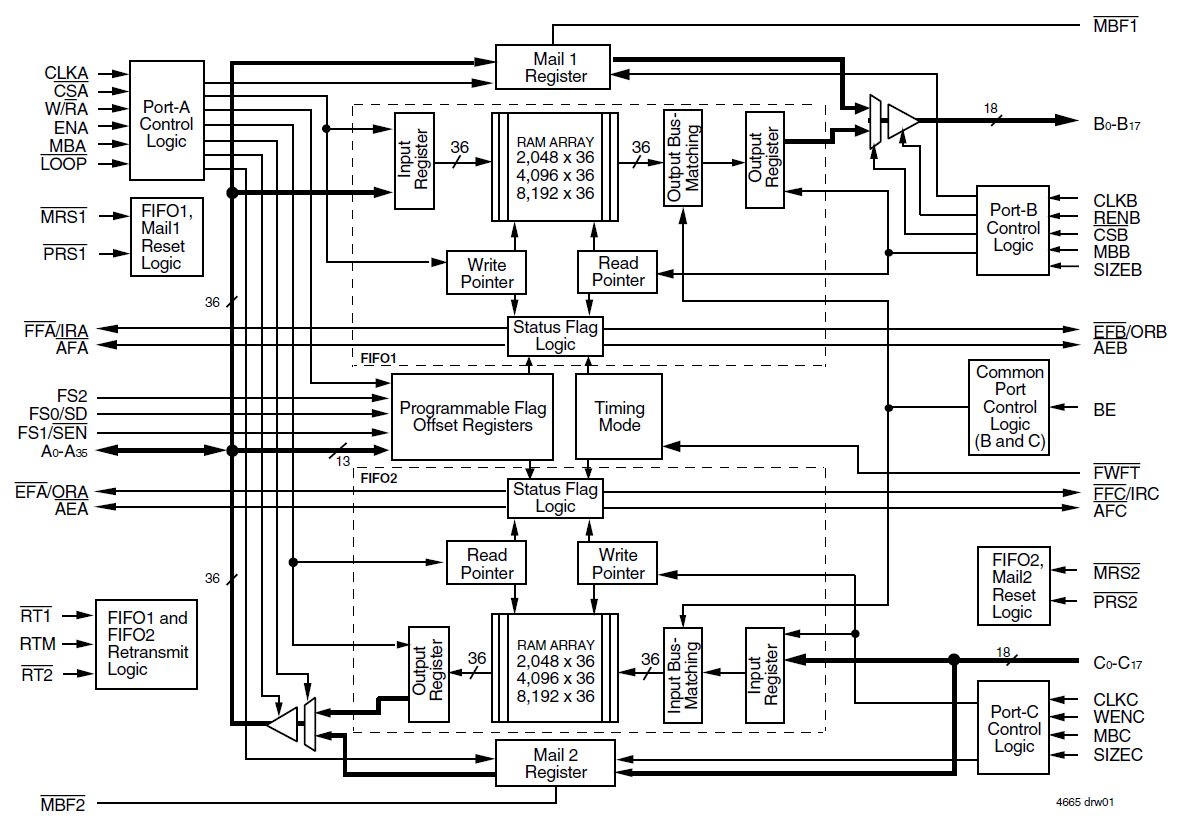

| Architecture | Bi-directional |

| Bus Width (bits) | 36 |

| Core Voltage (V) | 3.3 |

| Density (Kb) | 144 |

| Family Name | Triple-Bus FIFO |

| Function | Bus Matching |

| I/O Frequency (MHz) | 100 - 100 |

| I/O Type | 3.3 V LVTTL |

| Interface | Synchronous |

| Length (mm) | 20 |

| MOQ | 1000 |

| Moisture Sensitivity Level (MSL) | 3 |

| Organization | 2K x 36 x 2 |

| Package Area (mm²) | 280 |

| Pb Free Category | e0 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 20.0 x 14.0 x 1.4 |

| Pkg. Type | TQFP |

| Qty. per Carrier (#) | 0 |

| Qty. per Reel (#) | 1000 |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 14 |

| 已发布 | No |

有关 72V3656 的资源

描述

The 72V3656 is a 2K x 36 x 2 Triple Bus sync FIFO memory that is a 3.3V version of the 723656. The enables for each port are arranged to provide a simple bidirectional interface between microprocessors and/or buses with synchronous control. This device can operate in the IDT Standard mode or First Word Fall Through mode. Two 72V3656 FIFO's can be combined with unidirectional FIFO's capable of First Word Fall Through timing (i.e. the SuperSync FIFO family) to form a depth expansion.