封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | PP64 |

| Lead Count (#): | 64 |

| Pkg. Dimensions (mm): | 10.0 x 10.0 x 1.4 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Pb (Lead) Free | No |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Lead Count (#) | 64 |

| Pb (Lead) Free | No |

| Carrier Type | Tray |

| Architecture | Dual FIFO |

| Bus Width (bits) | 9 |

| Core Voltage (V) | 3.3 |

| Density (Kb) | 9 |

| Family Name | DualSync |

| I/O Frequency (MHz) | 66 - 66 |

| I/O Type | 3.3 V LVTTL |

| Interface | Synchronous |

| Length (mm) | 10 |

| MOQ | 80 |

| Moisture Sensitivity Level (MSL) | 3 |

| Organization | 1K x 9 |

| Package Area (mm²) | 100 |

| Pb Free Category | e0 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.4 |

| Pkg. Type | TQFP |

| Qty. per Carrier (#) | 160 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 10 |

| 已发布 | No |

有关 72V821 的资源

描述

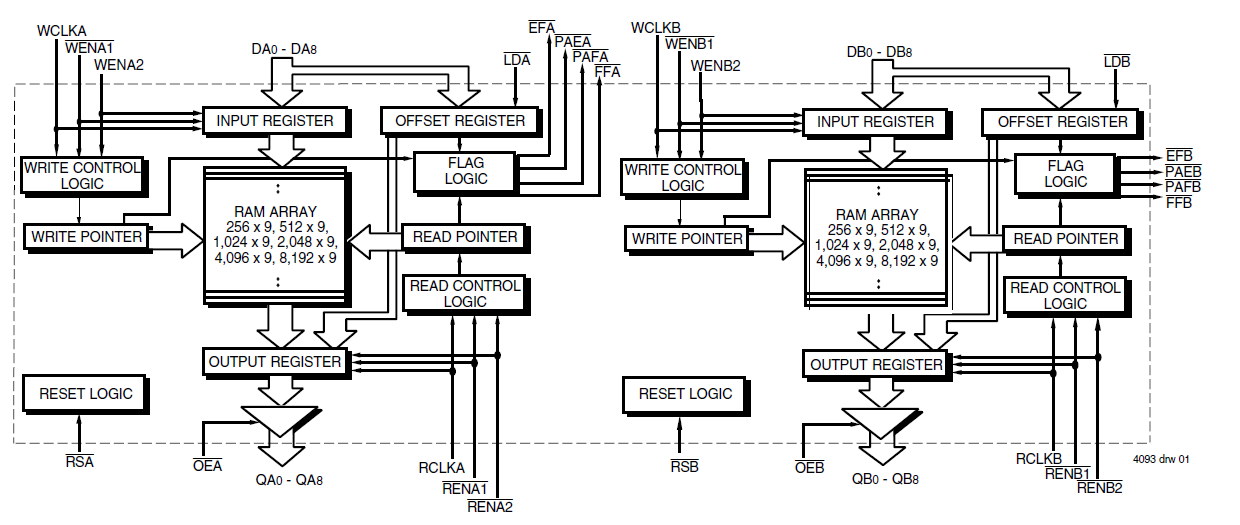

The 72V821is a 1K x 9 dual synchronous FIFO that is functionally equivalent to two 72V221 FIFOs in a single package with all associated control, data, and flag lines assigned to separate pins. Each FIFOs has a 9-bit input and output data port. The Read Clock can be tied to the Write Clock for single clock operation or the two clocks can run asynchronous of one another for dual clock operation.