封装信息

| CAD 模型: | View CAD Model |

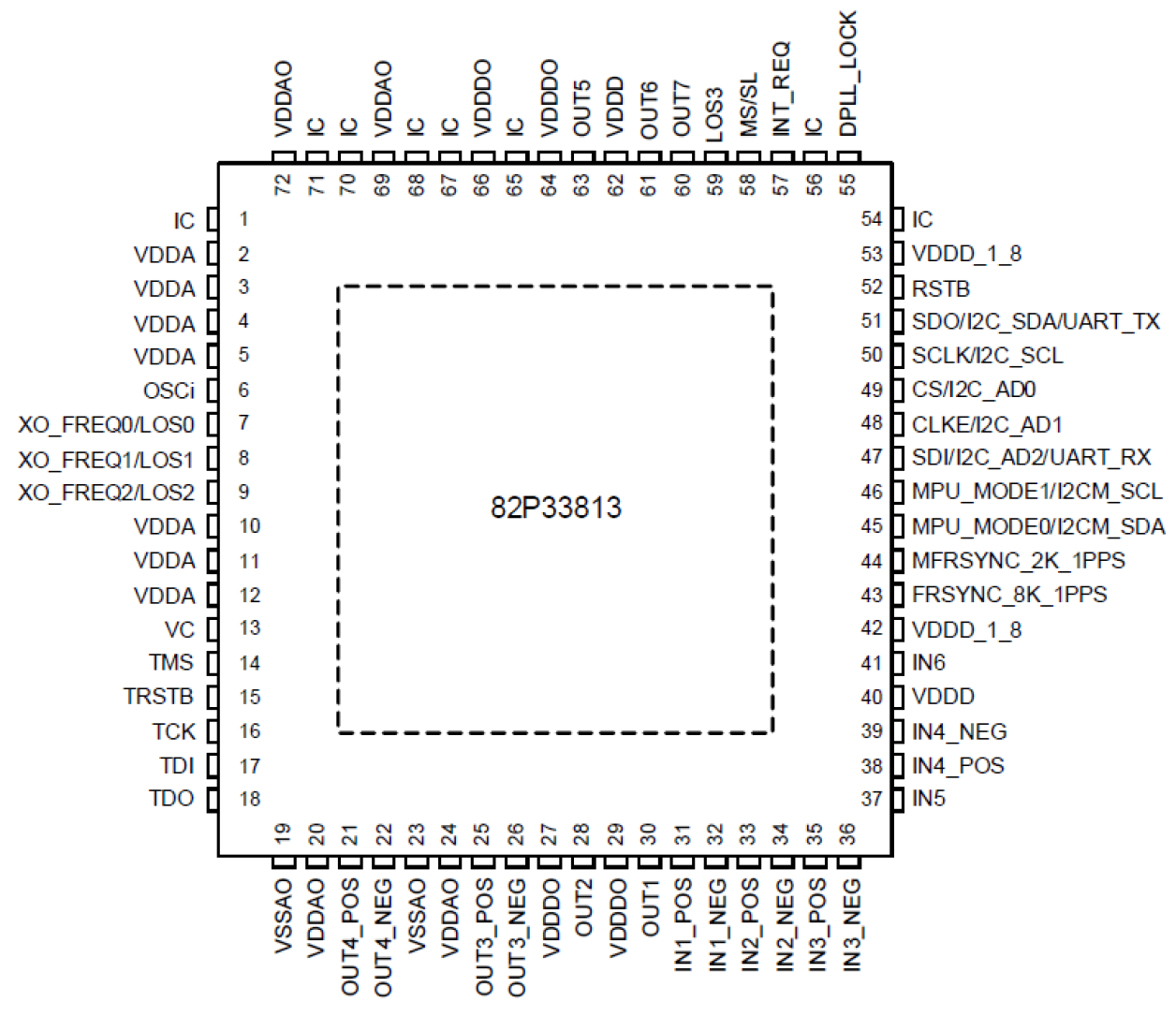

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG72 |

| Lead Count (#): | 72 |

| Pkg. Dimensions (mm): | 10.0 x 10.0 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 72 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 168 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Advanced Features | Full SETS (ITU-T G.8264), Hitless Reference Switching, Fractional-N Input Dividers, External Sync Input, External Feedback, DCO with Physical Layer Frequency Support, LOS Inputs |

| Application | System Synchronizer, IEEE 1588 Synthesizer |

| Channels (#) | 3 |

| Clock Support | G.813, G.8262, GR-1244-CORE, GR-253-CORE, G.8273.2 |

| Core Voltage (V) | 1.8 |

| Diff. Inputs | 4 |

| Diff. Outputs | 2 |

| Input Freq (MHz) | 1.0E-6 - 650 |

| Input Freq Range Type | 1PPS (1 Hz), TDM, DS1, E1, SONET/SDH, Ethernet, OTN, Sync Pulse |

| Input Type | LVCMOS, LVPECL, LVDS |

| Inputs (#) | 6 |

| Length (mm) | 10 |

| MOQ | 168 |

| Output Freq Range (MHz) | 1.0E-6 - 650 |

| Output Freq Range Type | 1PPS (1 Hz), TDM, DS1, E1, DS2, E3, DS3, 100BASE-T, STM-1/OC-3, STM-4/OC-12, 1000BASE-T/X, STM-16/OC-48 |

| Output Type | LVCMOS, LVPECL, LVDS |

| Outputs (#) | 9 |

| Package Area (mm²) | 100 |

| Phase Jitter Typ RMS (ps) | 0.56 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.0 |

| Pkg. Type | VFQFPN |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Thickness (mm) | 1 |

| Width (mm) | 10 |

| 已发布 | No |

有关 82P33813 的资源

描述

The 82P33813 Synchronization Management Unit (SMU) provides tools to manage timing references, clock sources, and timing paths for IEEE 1588/Precision Time Protocol (PTP) and Synchronous Ethernet (SyncE) based clocks. The device supports up to three independent timing paths that control: PTP clock synthesis; SyncE clock generation; and general-purpose frequency translation. It supports physical layer timing with Digital PLLs (DPLLs) and it supports packet-based timing with Digitally Controlled Oscillators (DCOs). Input-to-input, input-to-output and output-to-output phase skew can all be precisely managed. The device outputs low-jitter clocks that can directly synchronize lower-rate Ethernet interfaces; as well as CPRI/OBSAI, SONET/SDH, and PDH interfaces and IEEE 1588 Time Stamp Units (TSUs).