特性

- SMU allows any IEEE 1588 software, running on an external processor, to control the generation of electrical clocks, and to access and control physical layer synchronization

- Supports Telecom Boundary Clock (T-BC) and Telecom Time Slave Clock (T-TSC) applications per G.8273.2 with physical layer frequency support to the DCOs

- Physical layer clocks comply with ITU-T G.8262 for Synchronous Ethernet Equipment Clock (EEC), G.813 for Synchronous Equipment Clock (SEC), and Telcordia GR-253-CORE for Stratum 3 and SONET Minimum Clock (SMC)

- System-wide precise 1PPS (Pulse Per Second) edge alignment is supported with programmable input-to-input, input-to-output and output-to-output phase delays: sub-ns resolution

- 24-hour time holdover is supported by DCOs with fine frequency resolution (1.7e-16); Generates clocks for Ethernet, SONET/SDH, and PDH interfaces: jitter generation <1ps RMS (12kHz to 20MHz)

- IEEE 1588 grand master applications are supported by locking to 1PPS references from GPS or other GNSS sources

- Eases local oscillator sourcing by supporting any of eight common TCXO/OCXO frequencies for the system clock: 10MHz, 12.8MHz, 13MHz, 19.44MHz, 20MHz, 24.576MHz, 25MHz or 30.72MHz

- Automatically loads configuration from an external EPROM after reset without processor intervention

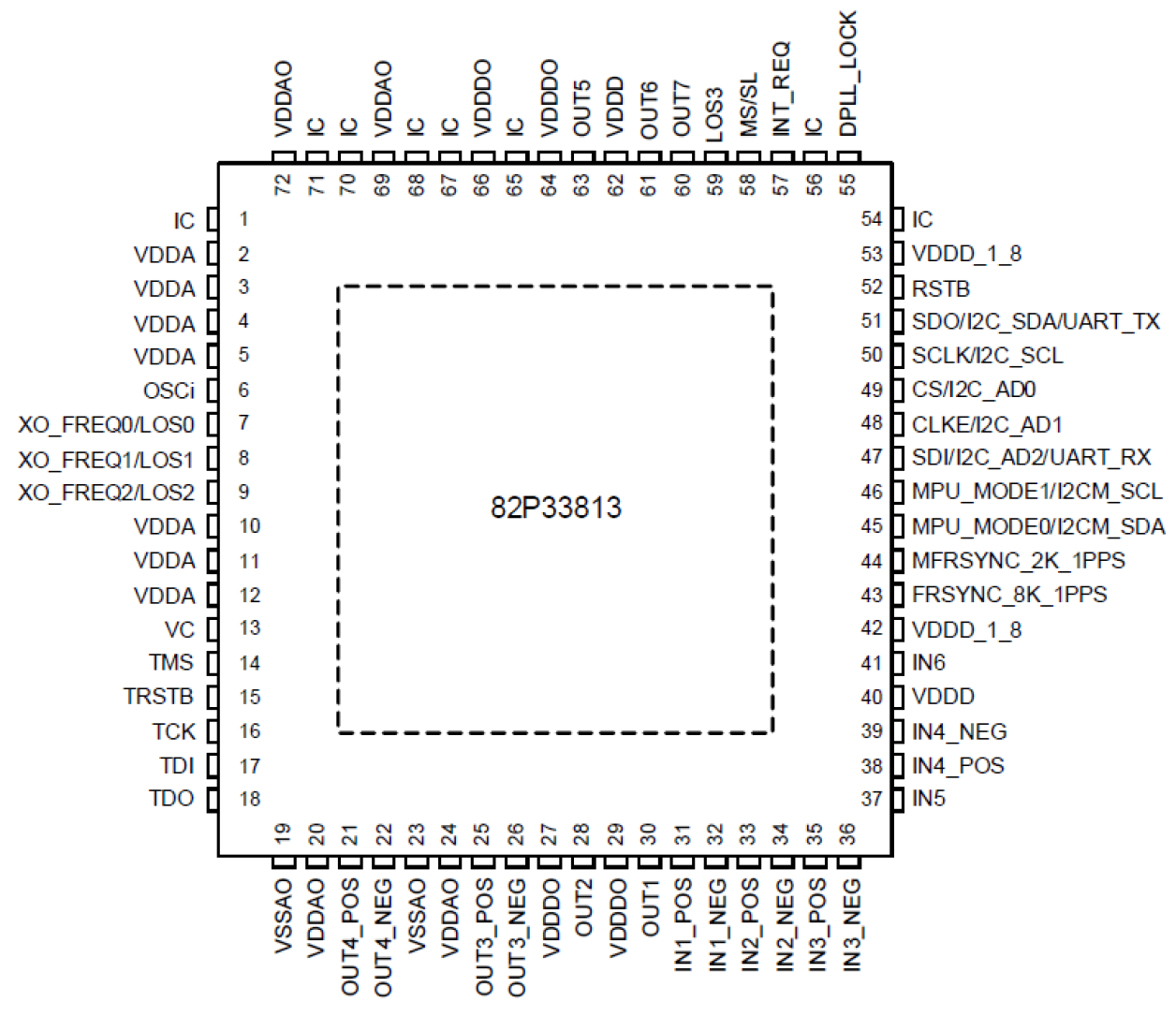

- 72-pin QFN package

描述

The 82P33813 Synchronization Management Unit (SMU) provides tools to manage timing references, clock sources, and timing paths for IEEE 1588/Precision Time Protocol (PTP) and Synchronous Ethernet (SyncE) based clocks. The device supports up to three independent timing paths that control: PTP clock synthesis; SyncE clock generation; and general-purpose frequency translation. It supports physical layer timing with Digital PLLs (DPLLs) and it supports packet-based timing with Digitally Controlled Oscillators (DCOs). Input-to-input, input-to-output and output-to-output phase skew can all be precisely managed. The device outputs low-jitter clocks that can directly synchronize lower-rate Ethernet interfaces; as well as CPRI/OBSAI, SONET/SDH, and PDH interfaces and IEEE 1588 Time Stamp Units (TSUs).

应用

- Access routers, edge routers, core routers

- Carrier Ethernet switches

- Multi-service access platforms

- Optical network terminal (ONT)

- Distribution point Unit (DPU)

- PON OLT

- LTE eNodeB

- IEEE 158/PTP Telecom Profile clock synthesizer

- ITU-T G.8273.2 Telecom Time Slave Clock (T-TSC)

- ITU-T G.8264 Synchronous Equipment Timing Source (SETS)

- ITU-T G.8263 Packet-based Equipment Clock (PEC)

- ITU-T G.8262 Synchronous Ethernet Equipment Clock (EEC)

- ITU-T G.813 Synchronous Equipment Clock (SEC)

- Telcordia GR-253-CORE Stratum 3 Clock (S3) and SONET Minimum Clock (SMC)