特性

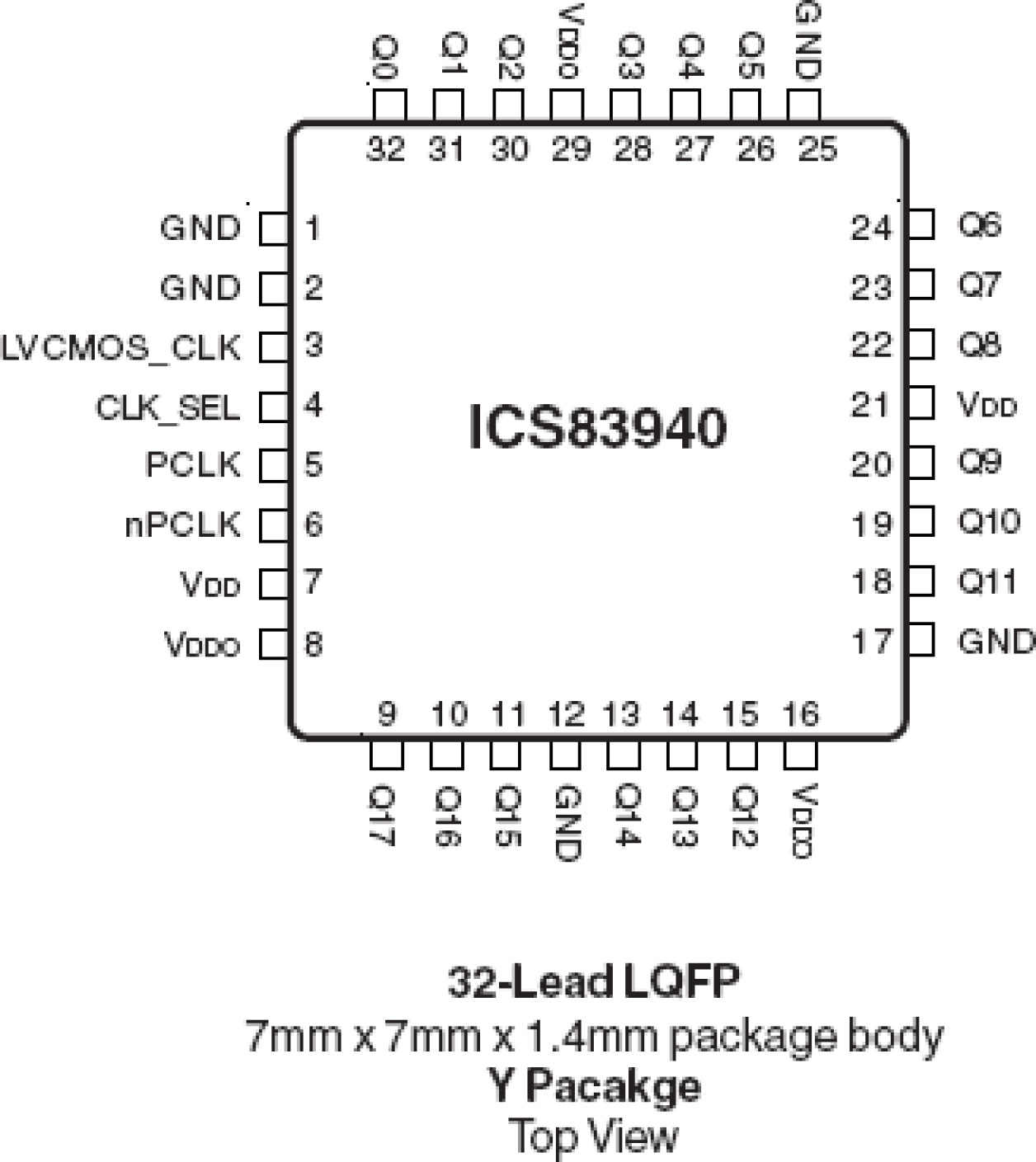

- Eighteen LVCMOS/LVTTL outputs, 16Ω typical output impedance

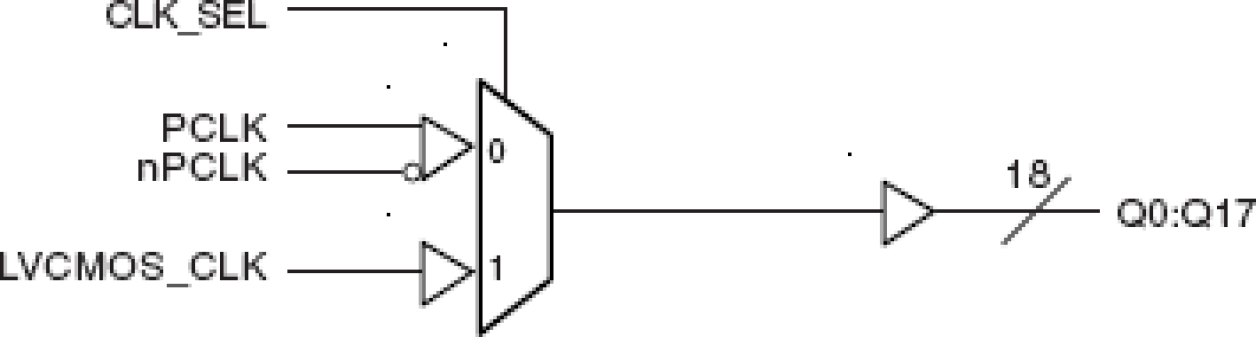

- Selectable LVCMOS_CLK or LVPECL clock inputs

- PCLK, nPCLK supports the following input types: LVPECL, CML, SSTL

- LVCMOS_CLK accepts the following input levels: LVCMOS or LVTTL

- Maximum output frequency: 250MHz

- Output skew: 150ps (maximum)

- Part to part skew: 750ps (maximum)

- Full 3.3V or 2.5V supply modes

- 0°C to 70°C ambient operating temperature

- Industrial temperature information available upon request

- Lead-Free package fully RoHS compliant

- NRND - Not Recommended for New Designs

For new designs use 83940D

描述

The 83940 is a low skew, 1-to-18 LVPECL-to-LVCMOS/ LVTTL Fanout Buffer. The 83940 has twoselectable clock inputs. The PCLK, nPCLK pair can accept LVPECL, CML, or SSTL input levels. The LVCMOS_CLK can accept LVCMOS or LVTTL input levels. The low impedance LVCMOS/LVTTL outputs are designed to drive 50Ω series or parallel terminated transmission lines. The 83940 is characterized at full 3.3V, full 2.5V and mixed 3.3V input and 2.5V output operating supply modes. Guaranteed output and part-to-part skew characteristics make the 83940 ideal for those clock distribution applications demanding well defined performance and repeatability.

当前筛选条件