封装信息

| CAD 模型: | View CAD Model |

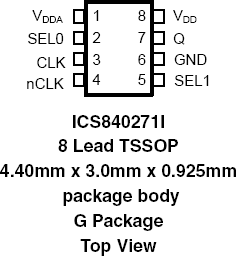

| Pkg. Type: | TSSOP |

| Pkg. Code: | PGG8 |

| Lead Count (#): | 8 |

| Pkg. Dimensions (mm): | 3.1 x 4.4 x 1.0 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 8 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 2500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| C-C Jitter Max P-P (ps) | 15 |

| Core Voltage (V) | 2.5V, 3.3V |

| Feedback Input | No |

| Input Freq (MHz) | 125 - 125, 156.25 - 156.25, 161.133 - 161.133 |

| Input Type | LVPECL, LVDS, HSTL, SSTL, HCSL |

| Inputs (#) | 1 |

| Length (mm) | 3.1 |

| MOQ | 2500 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 25 - 25 |

| Output Type | LVCMOS |

| Output Voltage (V) | 2.5V, 3.3V |

| Outputs (#) | 1 |

| Package Area (mm²) | 13.6 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 3.1 x 4.4 x 1.0 |

| Pkg. Type | TSSOP |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 4.4 |

| 已发布 | No |

有关 840271I 的资源

描述

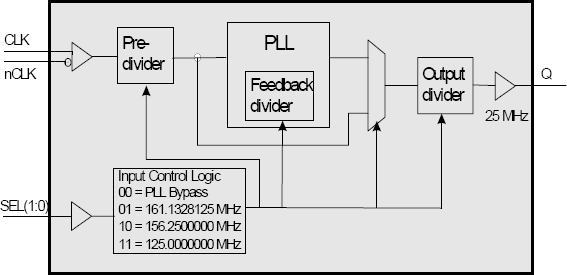

The 840271I is a PLL-based Frequency Translator intended for use in telecommunication applications such as Synchronous Ethernet. The internal PLL translates Ethernet clock frequencies such as 125MHz (1Gb Ethernet), 156.25MHz (10GbE XAUI) and 161.1328MHz (10Gb Ethernet) to an output frequency of 25MHz. The PLL does not any require external components. The input frequency is selectable by a 2-pin interface. The 840271I is optimized for low cycle-to-cycle jitter on the 25MHz output signal. The input of the device accepts differential (LVPECL, LVDS, LVHSTL, SSTL, HCSL) or single-ended (LVCMOS) signals. The extended temperature range supports telecommunication and networking equipment requirements. The 840271I uses a small RoHS 6, 8-pin TSSOP package and is an effective solution for space-constrained applications.