特性

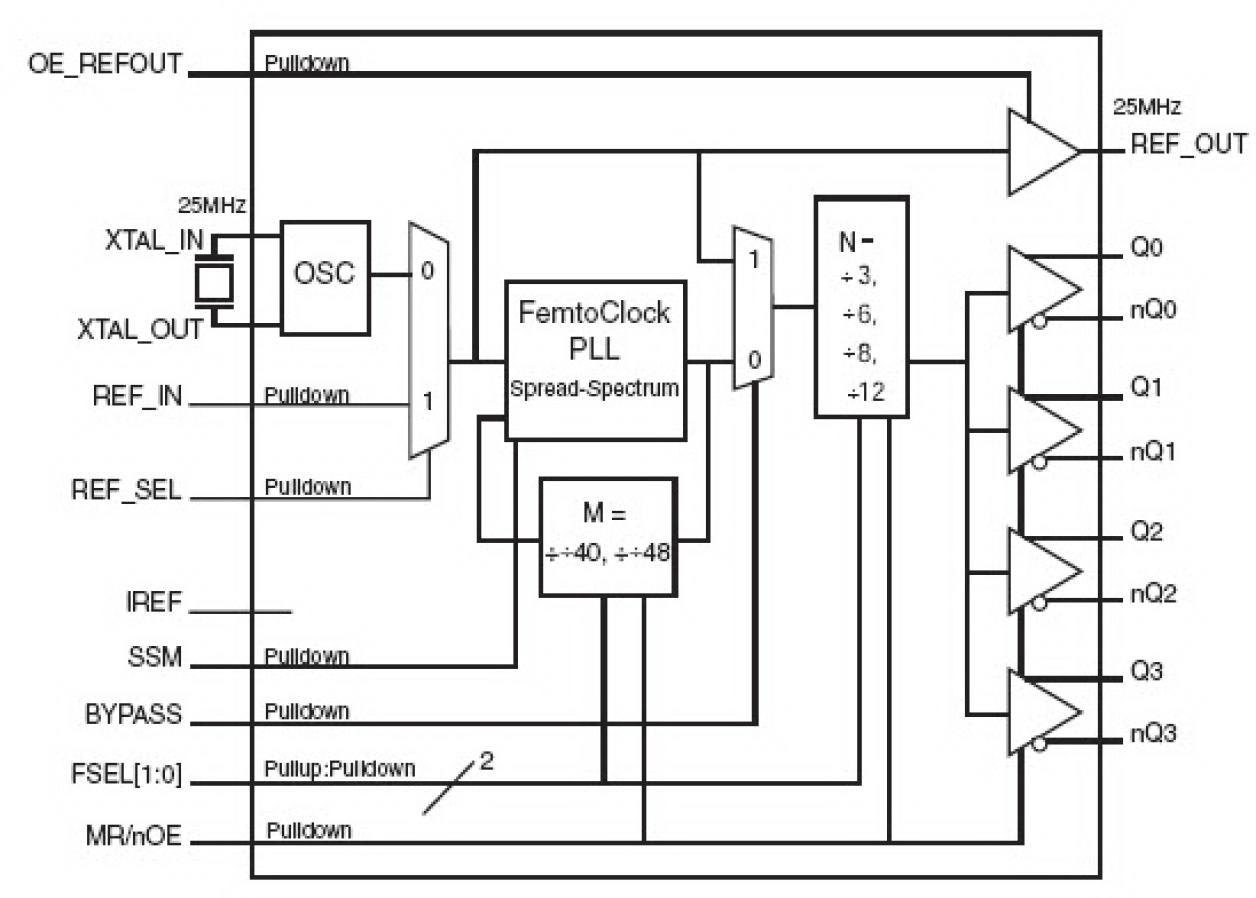

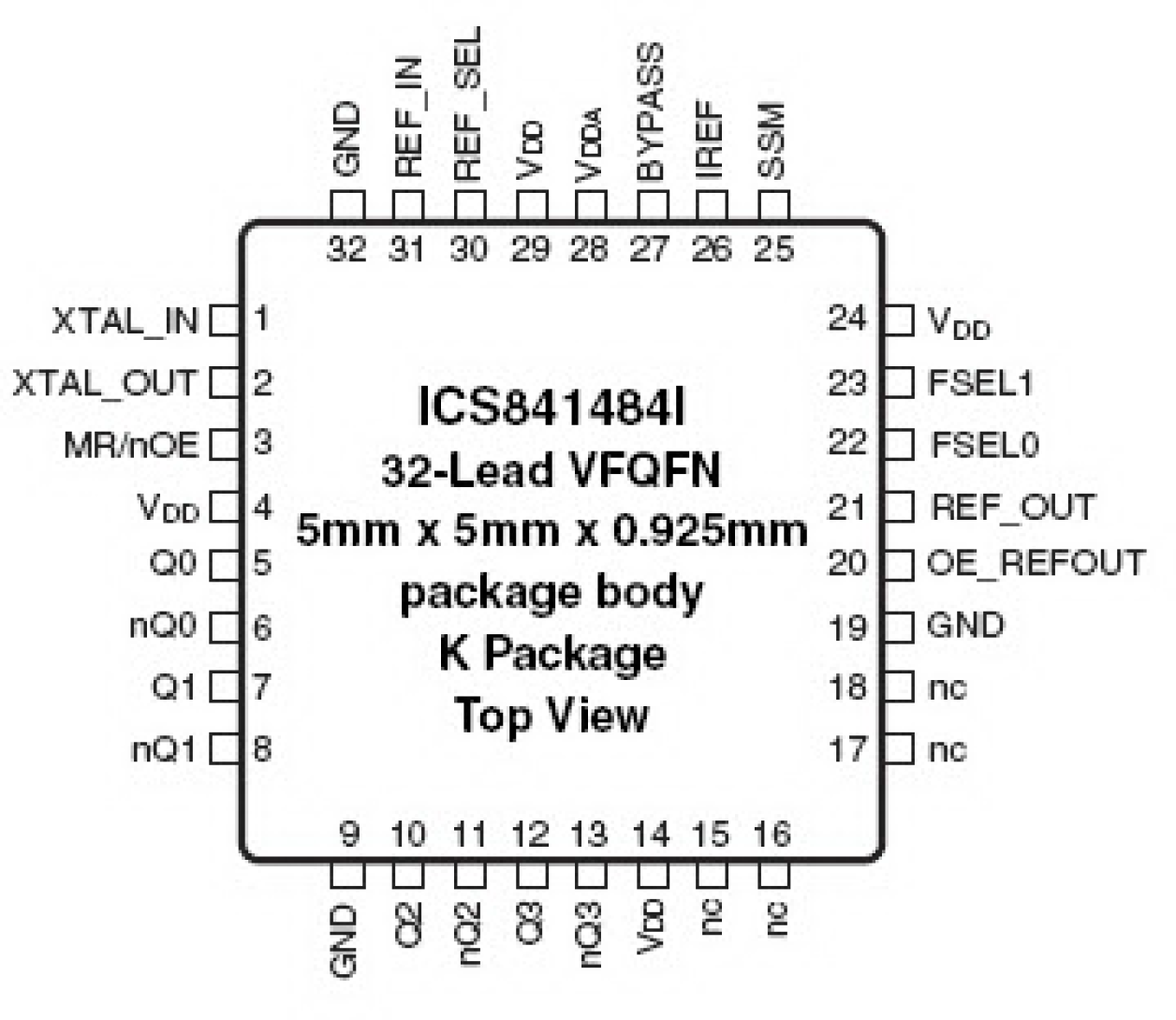

- Four 0.7V differential HCSL outputs: configurable for PCIe (100MHz or 200MHz) and sRIO (125MHz) clock signals

- One LVCMOS/LVTTL reference clock output

- Selectable crystal oscillator interface, 25MHz, 18pF parallel resonant crystal or LVCMOS/LVTTL single-ended reference clock input

- Supports the following output frequencies: 100MHz, 125MHz, 200MHz or 400MHz

- VCO frequency range: 950MHz - 1.25GHz

- Configurable spread-spectrum generation for PCIe

- PLL bypass and output enable

- RMS phase jitter @ 200MHz, using a 25MHz crystal (12kHz - 20MHz): 1.21ps (typical)

- PCI Express (2.5 Gb/S), Gen 2 (5 Gb/s) and Gen 3 (8 Gb/s) jitter compliant (REF_OUT disabled)

- Full 3.3V operating supply

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) packages

描述

The 841484I is an optimized PCIe and sRIO clock generator. The device uses a 25MHz parallel resonant crystal to generate 100MHz, 125MHz, 200MHz and 400MHz clock signals, replacing solutions requiring multiple oscillator and fanout buffer solutions. The device has excellent phase jitter suitable to clock components requiring precise and low jitter PCIe, sRIO or both clock signals. The device also supports a configurable spread-spectrum generation for PCIe applications. Designed for telecom, networking and industrial applications, the 841484I can also drive the high-speed sRIO and PCIe SerDes clock inputs of communications processors, DSPs, switches and bridges.

当前筛选条件