特性

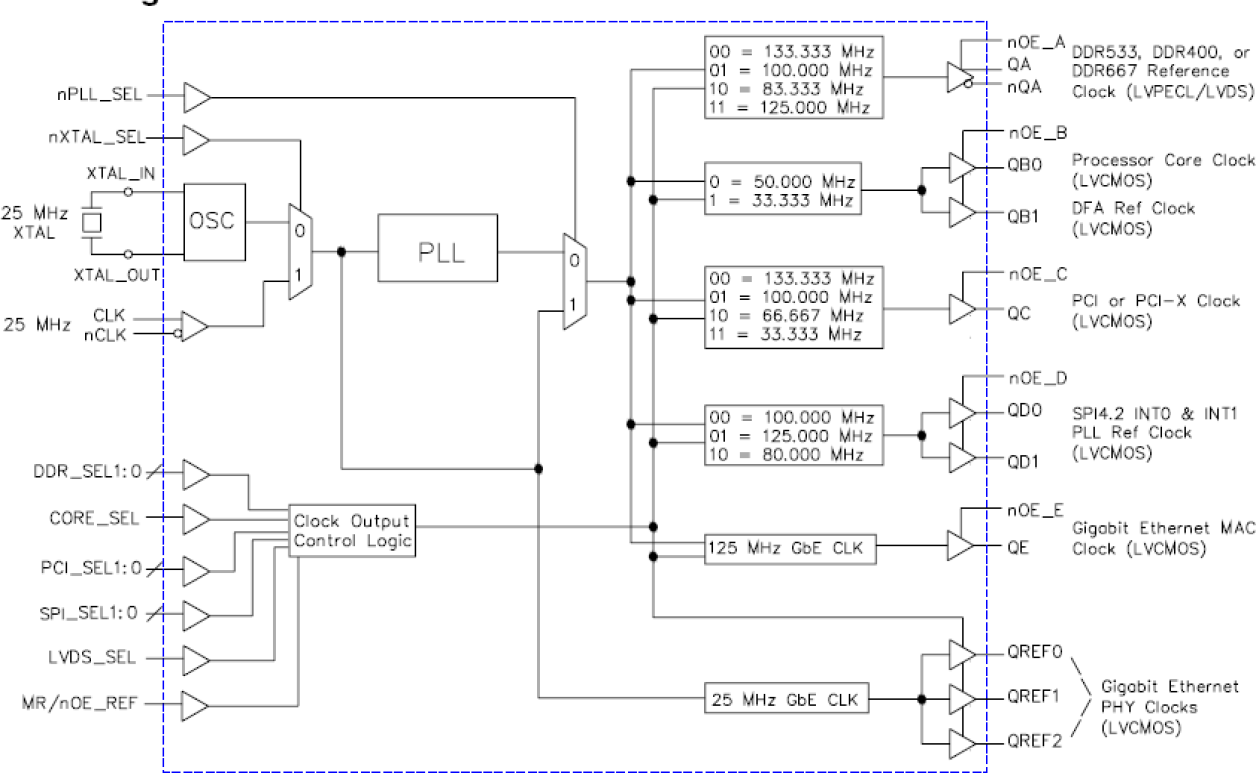

- One selectable clock for DDR 400/533/667, LVPECL/LVDS interface levels

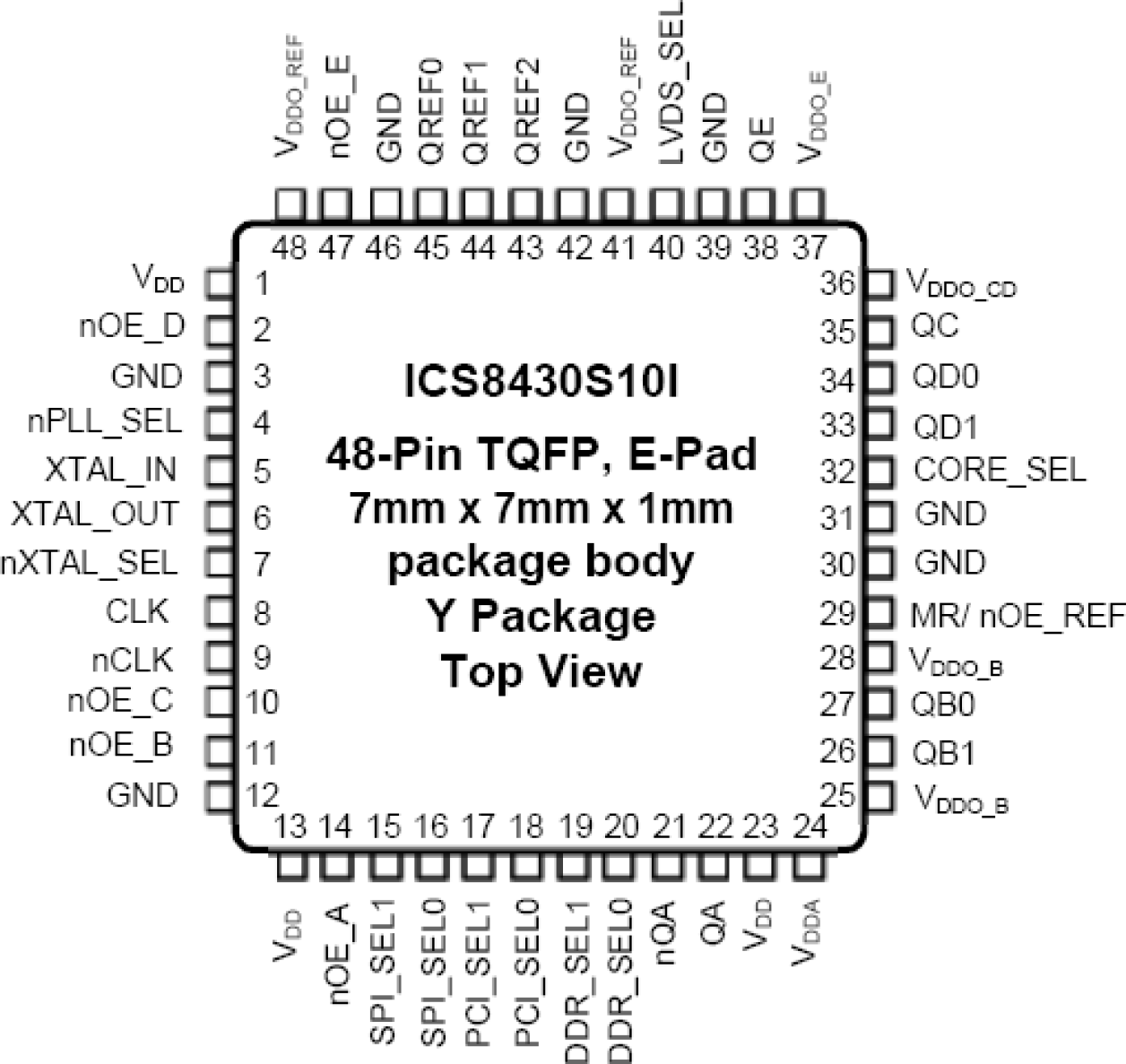

- Nine LVCMOS/ LVTTL outputs, 15Ω typical output impedance

- Selectable external crystal or differential input source

- Crystal oscillator interface designed for 25MHz, parallel resonant crystal

- Differential input pair (CLK, nCLK) accepts LVPECL, LVDS, SSTL input levels

- Internal resistor bias on nCLK pin allows the user to drive CLK input with external single-ended (LVCMOS/ LVTTL) input levels

- Power output supply modes LVDS and LVPECL - full 3.3V LVCMOS - full 3.3V or mixed 3.3V core/2.5V output

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

描述

The 8430S10I is a PLL-based clock generator specifically designed for Cavium Networks SoC processors. This high performance device is optimized to generate the processor core reference clock, the DDR reference clocks, the PCI/PCI-X bus clocks, and the clocks for both the Gigabit Ethernet MAC and PHY. The clock generator offers ultra low-jitter, low-skew clock outputs, and edge rates that easily meet the input requirements for the CN30XX/ CN31XX/CN38XX/CN58XX processors. The output frequencies are generated from a 25MHz external input source or an external 25MHz parallel resonant crystal. The extended temperature range of the 8430S10I supports telecommunication, networking, and storage requirements.

当前筛选条件