封装信息

| CAD 模型: | View CAD Model |

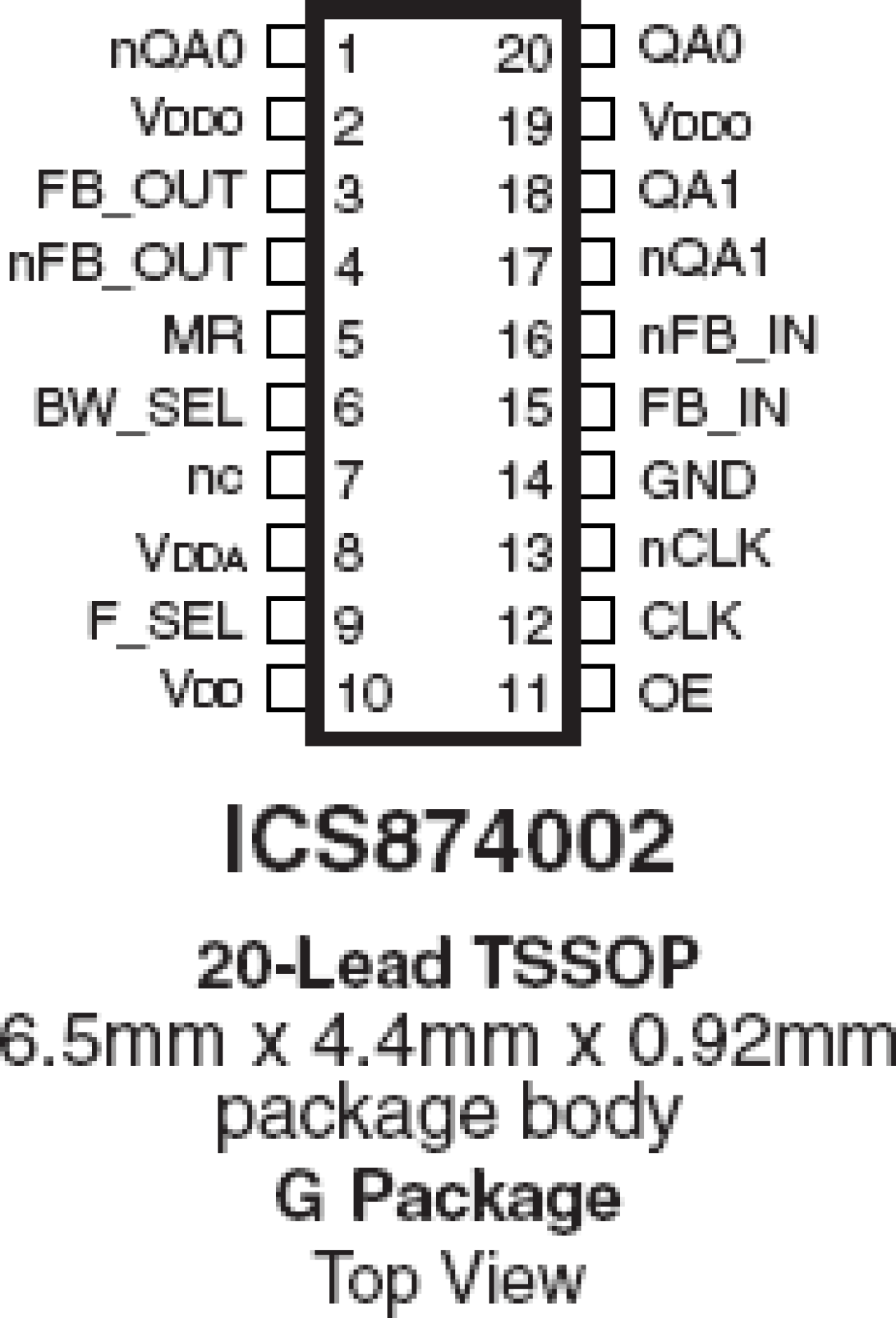

| Pkg. Type: | TSSOP |

| Pkg. Code: | PGG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 6.5 x 4.4 x 1.0 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 1 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | TSSOP |

| Lead Count (#) | 20 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tube |

| Advanced Features | Feedback Input, Spread Spectrum |

| App Jitter Compliance | PCIe |

| C-C Jitter Max P-P (ps) | 35 |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Freq (MHz) | 98 - 128 |

| Input Type | HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 1 |

| Length (mm) | 6.5 |

| MOQ | 74 |

| Moisture Sensitivity Level (MSL) | 1 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 98 - 160 |

| Output Skew (ps) | 40 |

| Output Type | LVDS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 3 |

| Package Area (mm²) | 28.6 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 6.5 x 4.4 x 1.0 |

| Price (USD) | $39.483 |

| Prog. Clock | No |

| Qty. per Carrier (#) | 74 |

| Qty. per Reel (#) | 0 |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | Yes |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1 |

| Width (mm) | 4.4 |

| 已发布 | No |

有关 874002 的资源

描述

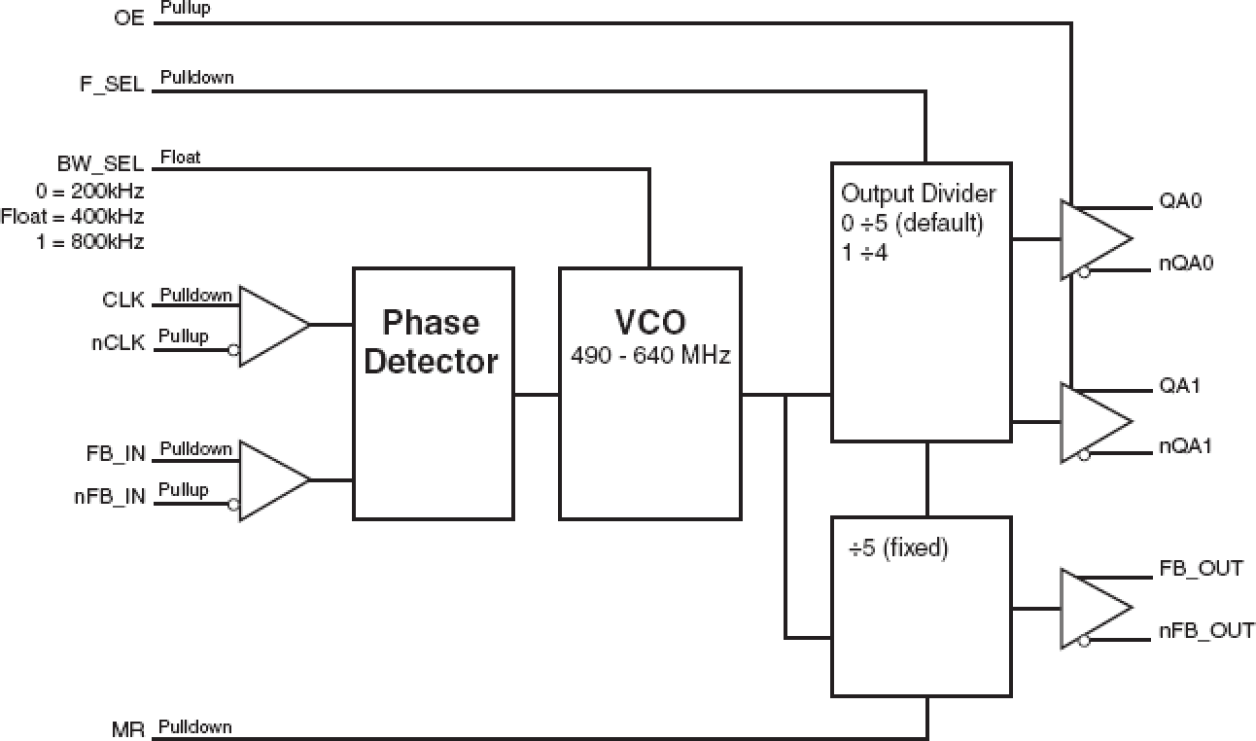

The 874002 is a high performance Differential-to-LVDS Jitter Attenuator designed for use in PCI Express® systems. In some PCI Express® systems, such as those found in desktop PCs, the PCI Express® clocks are generated from a low bandwidth, high phase noise PLL frequency synthesizer. In these systems, a jitter attenuator may be required to attenuate high frequency random and deterministic jitter components from the PLL synthesizer and from the system board. The 874002 has 3 PLL bandwidth modes: 200kHz, 400kHz, and 800kHz. The 200kHz mode will provide maximum jitter attenuation, but with higher PLL tracking skew and spread spectrum modulation from the motherboard synthesizer may be attenuated. The 400kHz provides an intermediate bandwidth that can easily track triangular spread profiles, while providing good jitter attenuation. The 800kHz bandwidth provides the best tracking skew and will pass most spread profiles, but the jitter attenuation will not be as good as the lower bandwidth modes. Because some 2.5Gb serdes have x20 multipliers while others have than x25 multipliers, the 874002 can be set for 1:1 mode or 5/4 multiplication mode (i.e. 100MHz input/125MHz output) using the F_SEL pin. The 874002 uses IDT's 3rd Generation FemtoClockTM PLL technology to achieve the lowest possible phase noise. The device is packaged in a 20 Lead TSSOP package, making it ideal for use in space constrained applications such as PCI Express® add-in cards.