封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG16 |

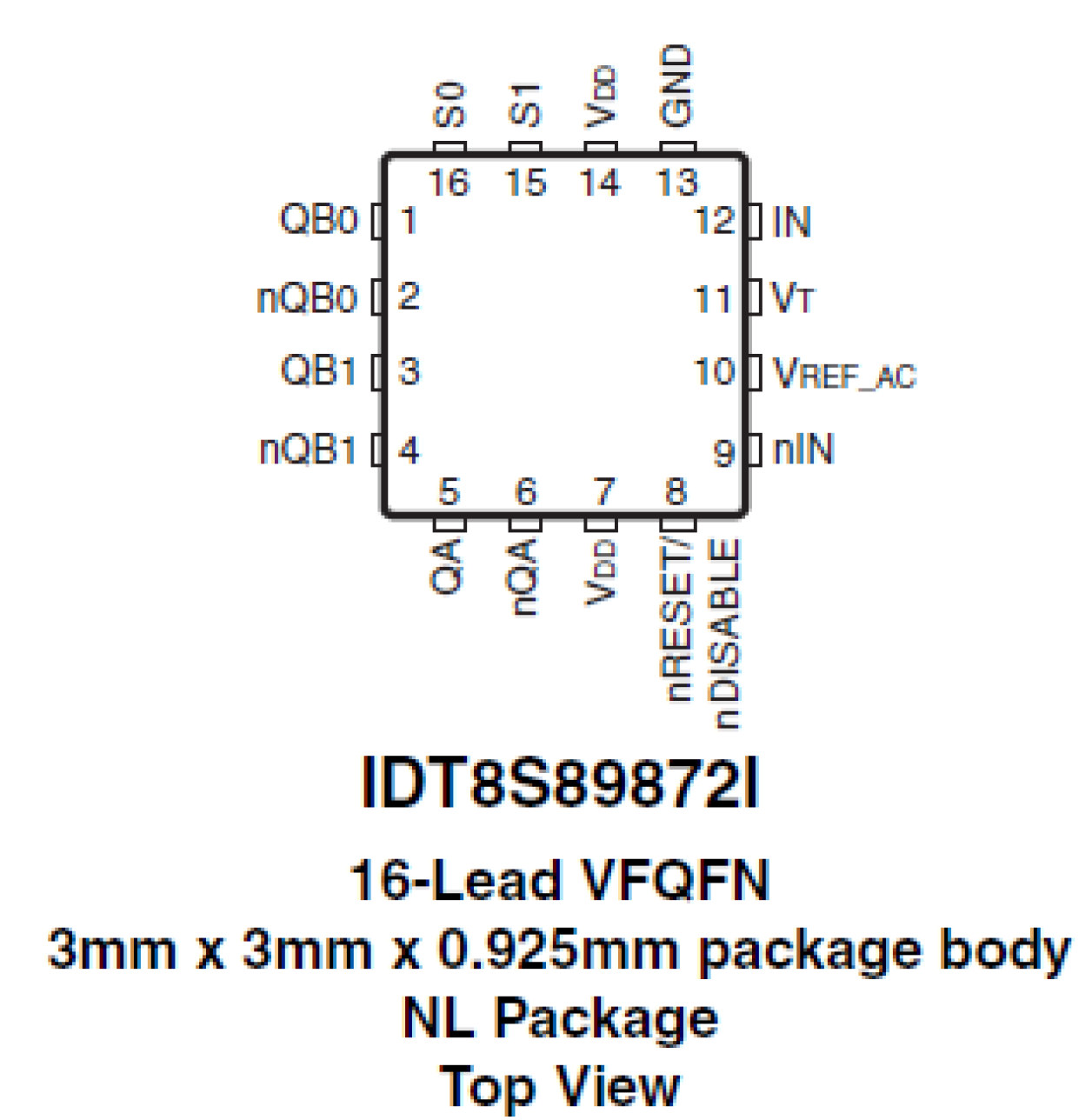

| Lead Count (#): | 16 |

| Pkg. Dimensions (mm): | 3.0 x 3.0 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | VFQFPN |

| Lead Count (#) | 16 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tray |

| Additive Phase Jitter Typ RMS (fs) | 150 |

| Additive Phase Jitter Typ RMS (ps) | 0.15 |

| Adjustable Phase | No |

| Channels (#) | 1 |

| Core Voltage (V) | 2.5V, 3.3V |

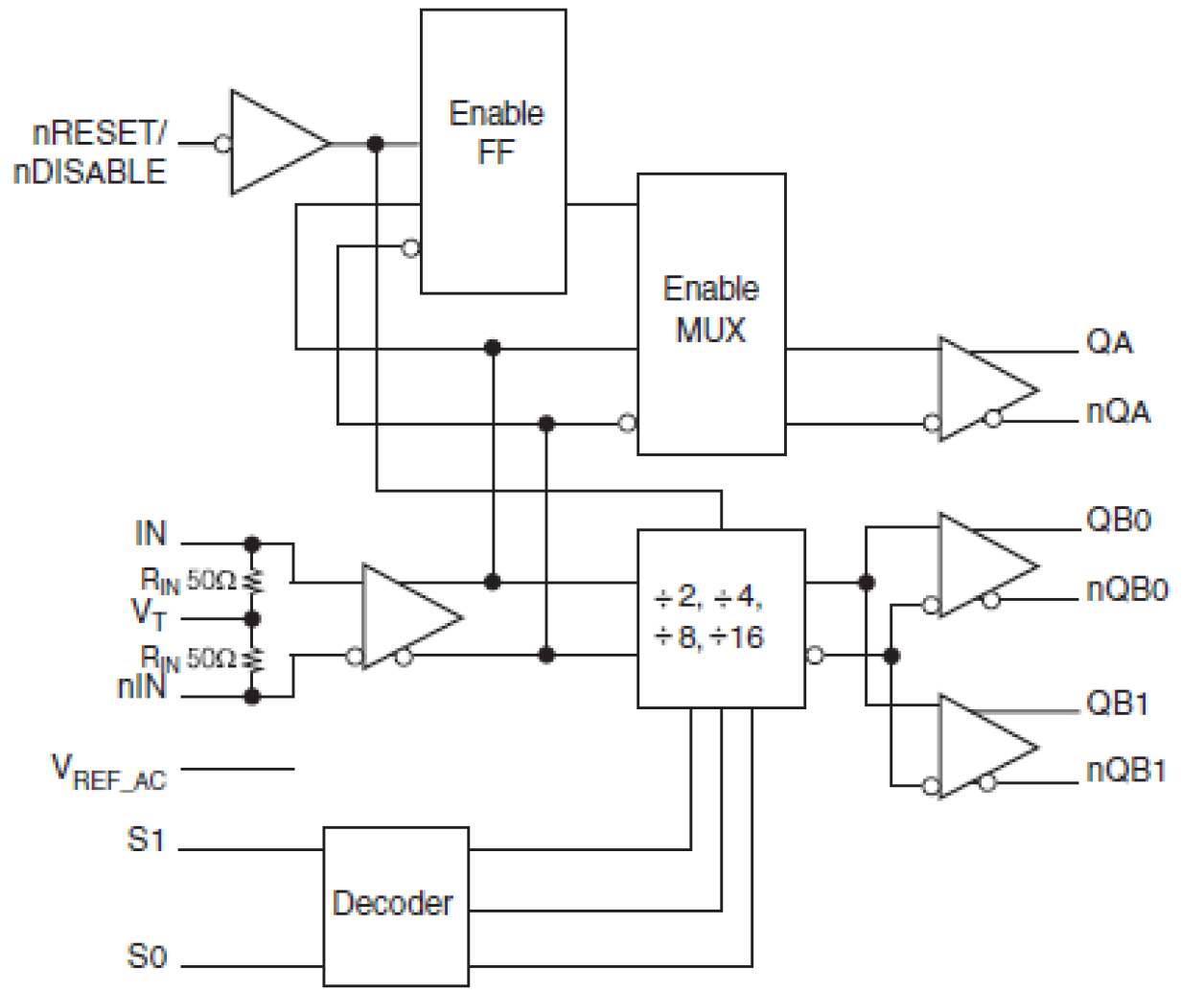

| Divider Value | 2, 4, 8, 16 |

| Function | Buffer, Divider |

| Input Freq (MHz) | 0 - 0 |

| Input Type | CML, LVDS, LVPECL |

| Inputs (#) | 1 |

| Length (mm) | 3 |

| MOQ | 200 |

| Moisture Sensitivity Level (MSL) | 3 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 2000 |

| Output Skew (ps) | 30 |

| Output Type | LVDS |

| Output Voltage (V) | 2.5V, 3.3V |

| Outputs (#) | 3 |

| Package Area (mm²) | 9 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 3.0 x 3.0 x 1.0 |

| Qty. per Carrier (#) | 624 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Supply Voltage (V) | 2.38 - 2.38, 2.63 - 2.63 |

| Tape & Reel | No |

| Temp. Range (°C) | -40 to 85°C |

| Thickness (mm) | 1 |

| Width (mm) | 3 |

| 已发布 | No |

有关 8S89872 的资源

描述

The 8S89872 is a high-speed Differential-to-LVDS Buffer/Divider with Internal Termination. The 8S89872 has a selectable ÷2, ÷4, ÷8, ÷16 output dividers. The clock input has internal termination resistors allowing it to interface with several differential signal types while minimizing the number of required external components. The device is packaged in a small, 3mm x 3mm VFQFN package, making it ideal for use on space-constrained boards.