封装信息

| CAD 模型: | View CAD Model |

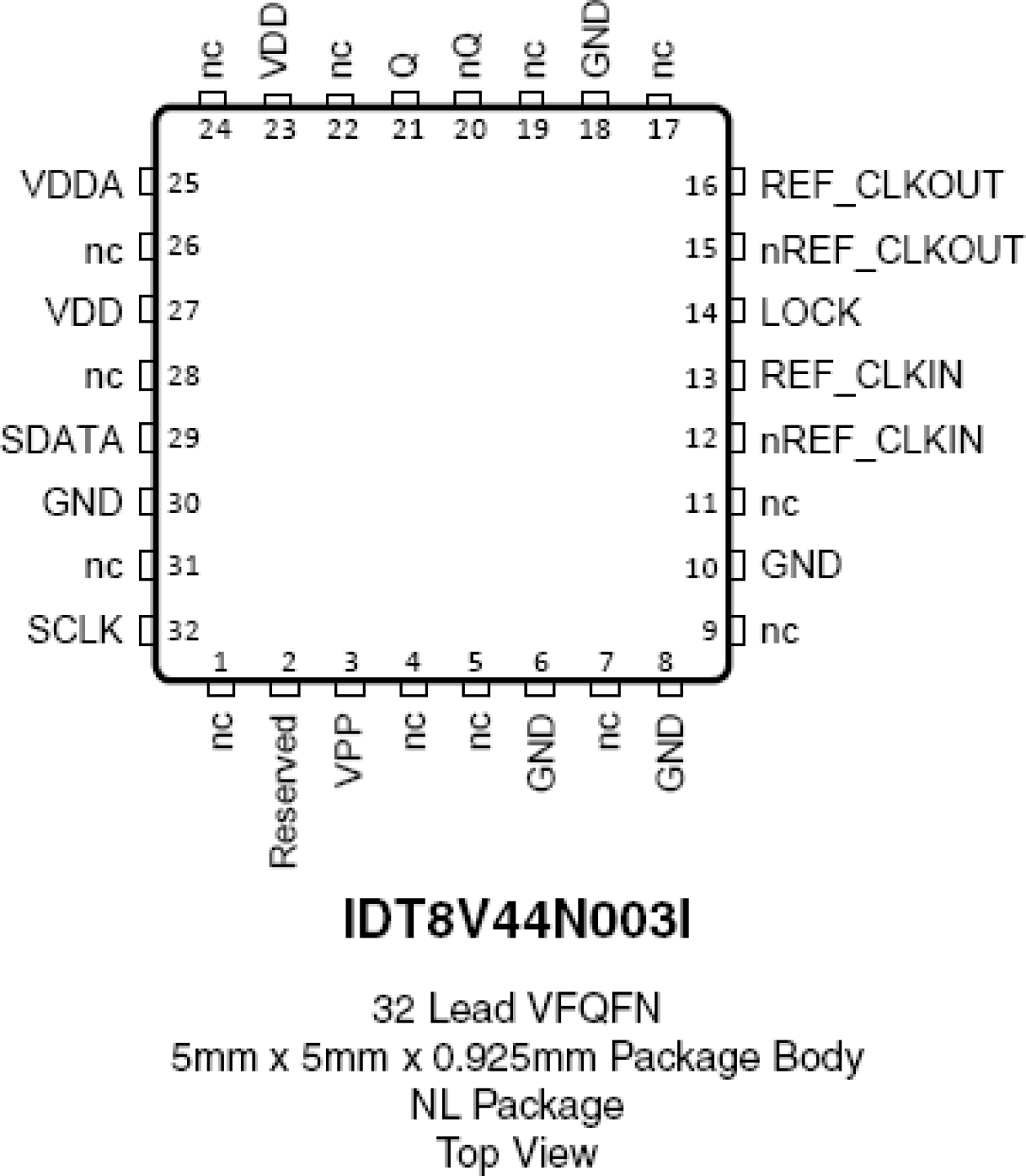

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG32 |

| Lead Count (#): | 32 |

| Pkg. Dimensions (mm): | 5.0 x 5.0 x 0.9 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 32 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 490 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Advanced Features | Programmable Clock, Reference Output |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 20 - 500 |

| Input Type | HCSL, LVDS, LVPECL, Sine Wave, LVCMOS |

| Inputs (#) | 1 |

| Length (mm) | 5 |

| MOQ | 490 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 50 - 1200 |

| Output Type | LVDS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 2 |

| Package Area (mm²) | 25 |

| Phase Jitter Max RMS (ps) | 0.45 |

| Phase Jitter Typ RMS (ps) | 0.3 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 5.0 x 5.0 x 0.9 |

| Pkg. Type | VFQFPN |

| Product Category | FemtoClock, Ultra-Low Jitter Clocks (<300 fs RMS) |

| Prog. Clock | Yes |

| Prog. Interface | I2C |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | No |

| Thickness (mm) | 0.9 |

| Width (mm) | 5 |

有关 8V44N003I 的资源

描述

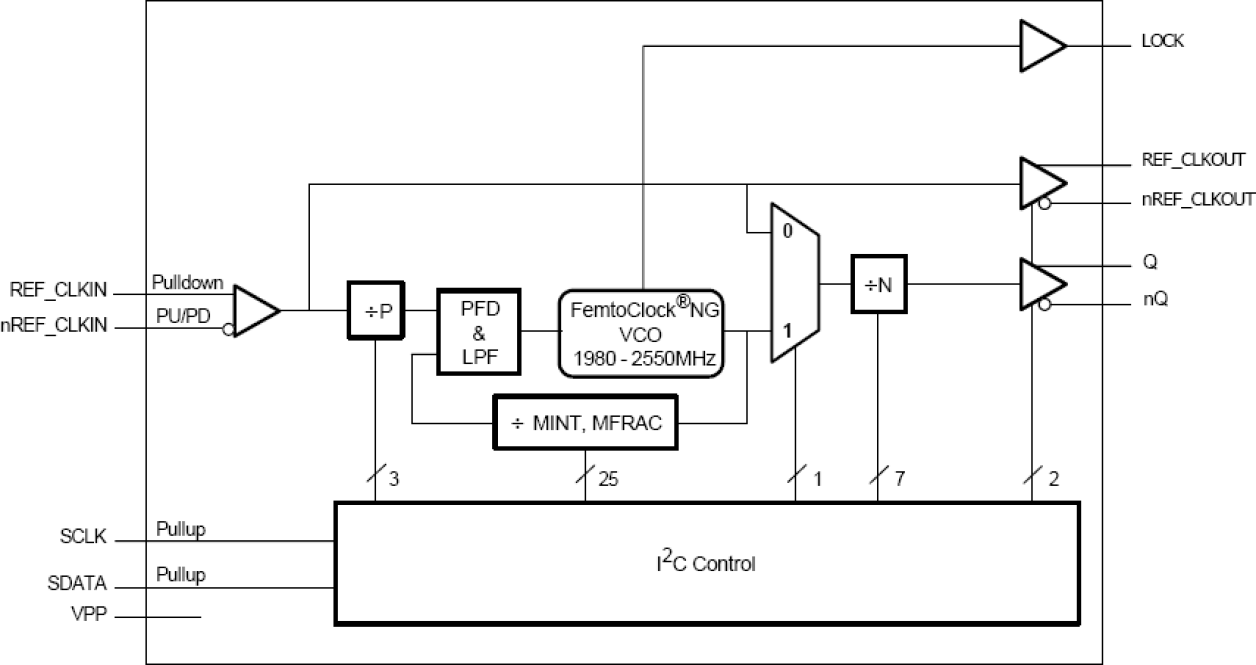

The 8V44N003I is a programmable LVDS synthesizer designed for applications requiring frequency conversion from a differential or single-end reference source. The device is designed to provide optimum performance of low phase noise and high power supply noise rejection over a wide range of output frequencies. Oscillator level phase noise performance is achieved through the use of Renesas' Fourth Generation FemtoClock™ NG PLL technology. Default output frequency settings are factory programmable via a one time programmable ROM while the I2C interface can be used to program the output frequency after power up. A buffered copy of the input reference clock is provided at both LVDS output levels for applications requiring efficient board space utilization.