特性

- Power up default is all outputs in 1:1 mode

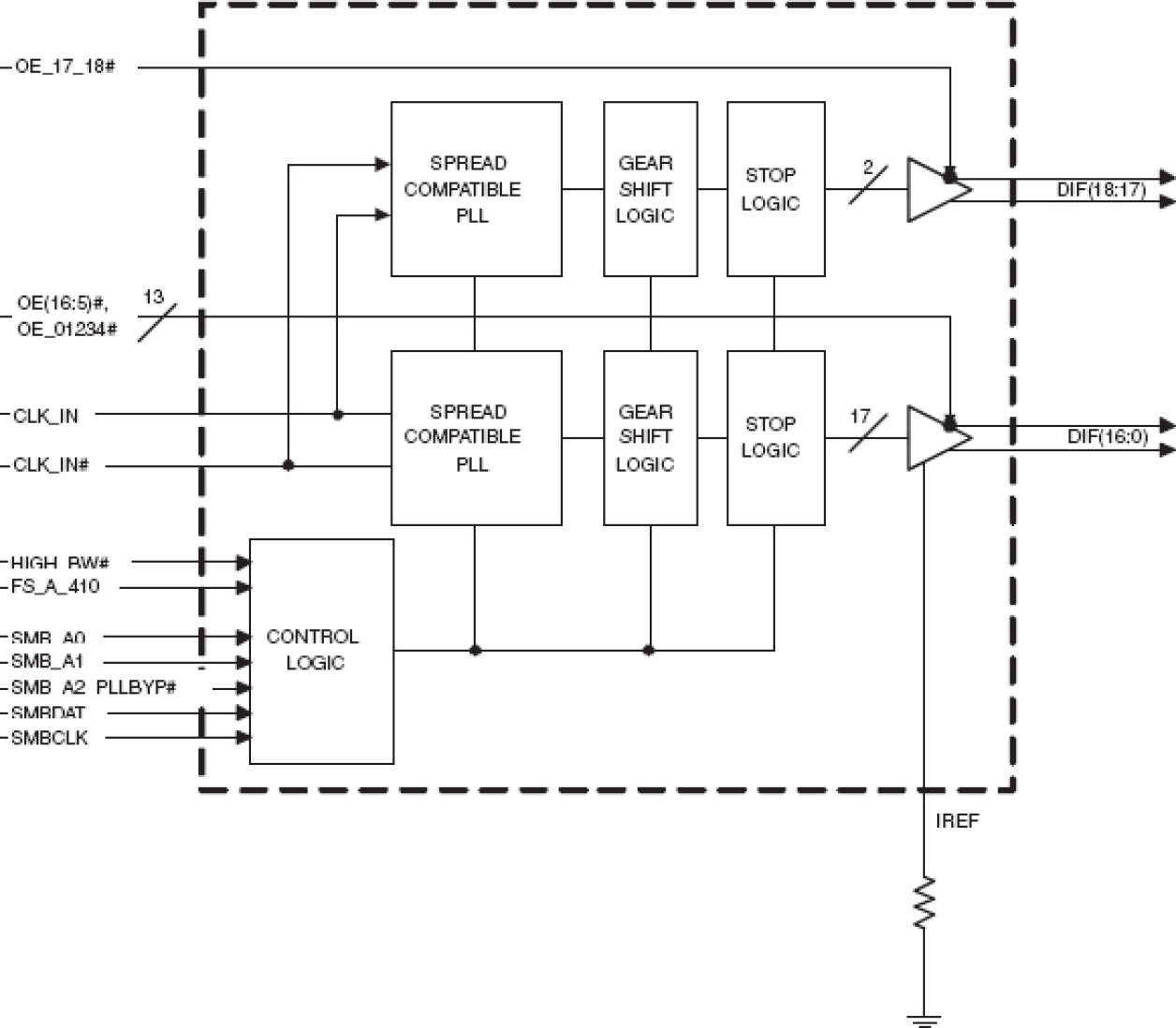

- DIF_(16:0) can be "gear-shifted" from the input CPU Host Clock

- DIF_(18:17) can be "gear-shifted" from the input CPU Host Clock

- Spread spectrum compatible

- Supports output clock frequencies up to 400 MHz

- 8 Selectable SMBus addresses

- SMBus address determines PLL or Bypass mode

- VDDA controlled power down mode

描述

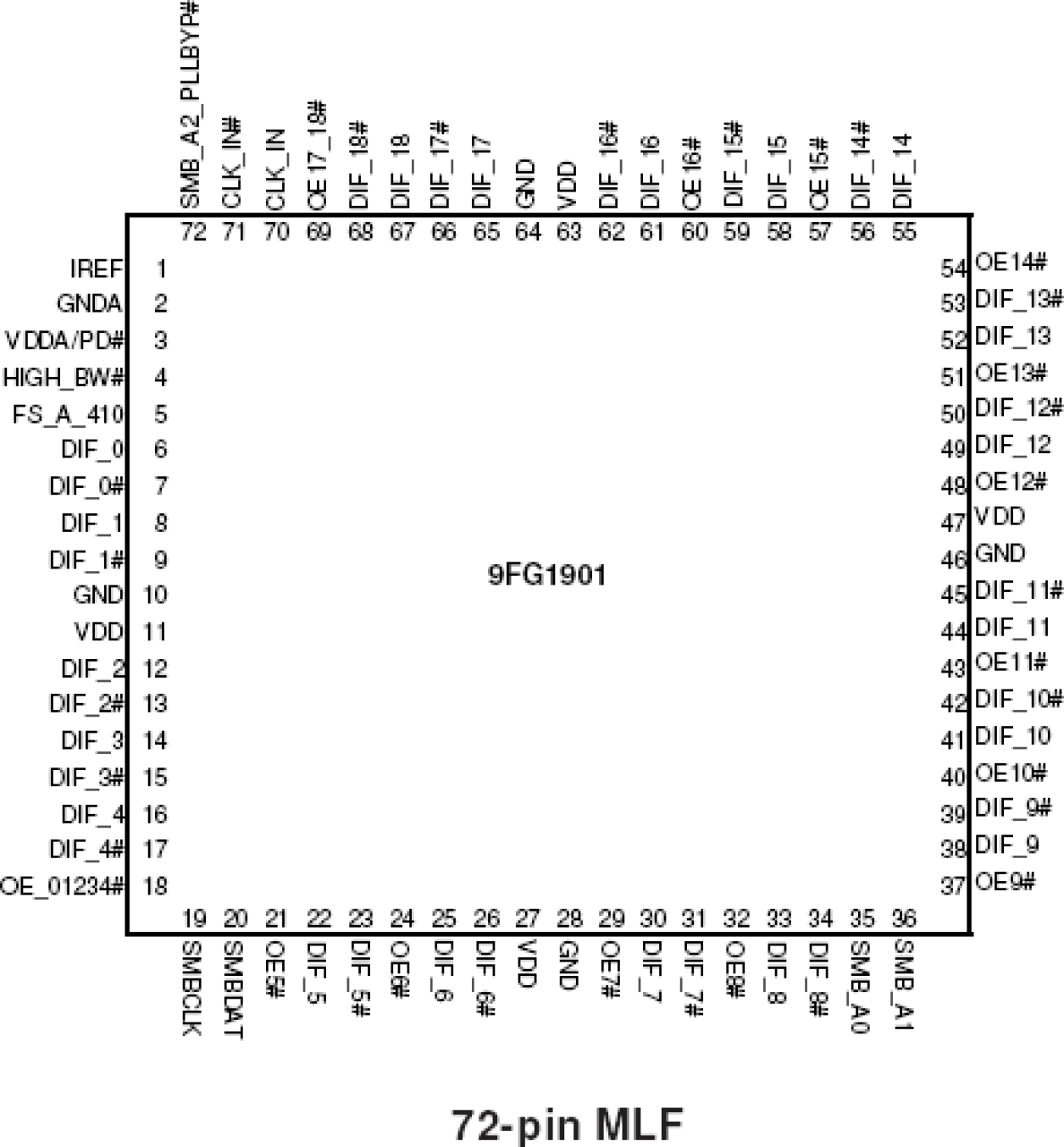

The IDT9FG1901 follows the Intel DB1900G Differential Buffer Specification. This buffer provides 19 output clocks for CPU Host Bus, PCI-Express, or Fully Buffered DIMM applications. The outputs are configured with two groups. Both groups, DIF_(16:0) and DIF_(18:17) can be equal to or have a gear ratio to the input clock. A differential CPU clock from a CK410B+ main clock generator, such as the IDT932S421, drives the IDT9FG1901. The IDT9FG1901 can provide outputs up to 400MHz.

当前筛选条件