封装信息

| CAD 模型: | View CAD Model |

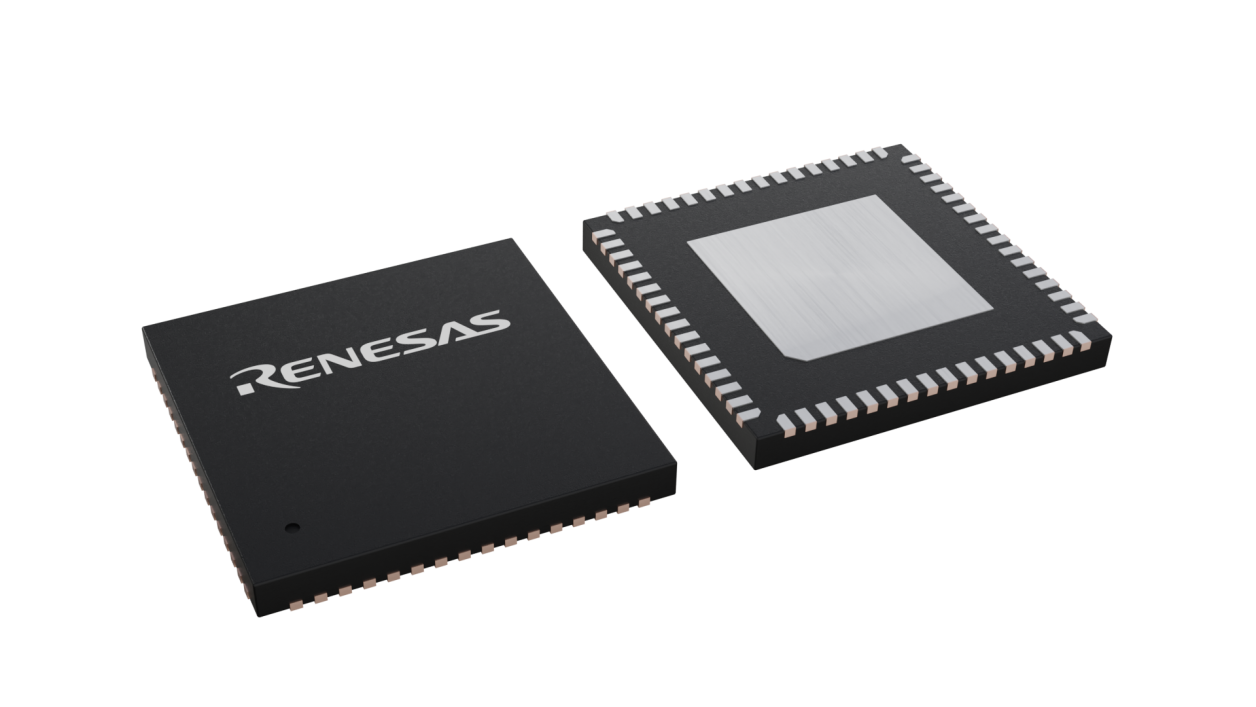

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG64 |

| Lead Count (#): | 64 |

| Pkg. Dimensions (mm): | 9.0 x 9.0 x 0.9 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 64 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 1000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Accepts Spread Spec Input | Yes |

| Advanced Features | SW PLL mode control |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3, PCIe Gen4, QPI, UPI, 25G EDR, IF-UPI, PCIe Gen5, DB2000Q |

| Architecture | Common, SRIS, SRNS |

| C-C Jitter Max P-P (ps) | 50 |

| Chipset Manufacturer | Intel |

| Chipset Name | C600, Patsburg, Wellsburg, Lewisburg |

| Clock Spec. | DB1200ZL v0.8 |

| Core Voltage (V) | 3.3V |

| Diff. Input Signaling | HCSL |

| Diff. Inputs | 1 |

| Diff. Output Signaling | LP-HCSL |

| Diff. Outputs | 12 |

| Diff. Termination Resistors | 24 |

| Feedback Input | No |

| Function | Zero Delay Buffer |

| Input Freq (MHz) | 33 - 150 |

| Input Type | HCSL |

| Inputs (#) | 1 |

| Length (mm) | 9 |

| MOQ | 1000 |

| Output Banks (#) | 1 |

| Output Enable (OE) Pins | 12 |

| Output Freq Range (MHz) | 1 - 400 |

| Output Impedance | 33 |

| Output Skew (ps) | 50 |

| Output Type | LP-HCSL |

| Output Voltage (V) | 0.7V |

| Outputs (#) | 12 |

| PLL | Yes |

| Package Area (mm²) | 81 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 9.0 x 9.0 x 0.9 |

| Pkg. Type | VFQFPN |

| Power Consumption Typ (mW) | 481 |

| Product Category | PCI Express Clocks, Processor Clock Buffers, Zero Delay Buffers |

| Prog. Clock | Yes |

| Prog. Interface | SMBUS |

| Reel Size (in) | 13 |

| Reference Output | No |

| Spread Spectrum | Yes |

| Supply Voltage (V) | 3.3 - 3.3 |

| Tape & Reel | Yes |

| Thickness (mm) | 0.9 |

| Width (mm) | 9 |

有关 9ZXL1231E 的资源

描述

The 9ZXL1231E is a second-generation, enhanced-performance DB1200ZL differential buffer. The part is a pin-compatible upgrade to the 9ZXL1231A while offering much-improved phase jitter performance and increased system security features. A fixed external feedback maintains low drift for critical QPI/UPI applications.