封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | SBDIP |

| Pkg. Code: | DAV |

| Lead Count (#): | 16 |

| Pkg. Dimensions (mm): | 20.32 x 7.49 x 2.41 |

| Pitch (mm): | 2.54 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pb (Lead) Free | Exempt |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | SBDIP |

| Lead Count (#) | 16 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pitch (mm) | 2.5 |

| Pkg. Dimensions (mm) | 20.3 x 7.5 x 2.41 |

| DLA SMD | 5962R9662401VEC |

| Pb (Lead) Free | Exempt |

| Pb Free Category | Gold Plate over compliant Undercoat-e4 |

| MOQ | 25 |

| Temp. Range (°C) | -55 to +125°C |

| DSEE (MeV·cm2/mg) | 75 |

| Length (mm) | 20.3 |

| Qualification Level | QML Class V (space) |

| Rating | Space |

| TID HDR (krad(Si)) | 100 |

| TID LDR (krad(Si)) | ELDRS free |

| Thickness (mm) | 2.41 |

| Width (mm) | 7.5 |

有关 CD4015BMS 的资源

描述

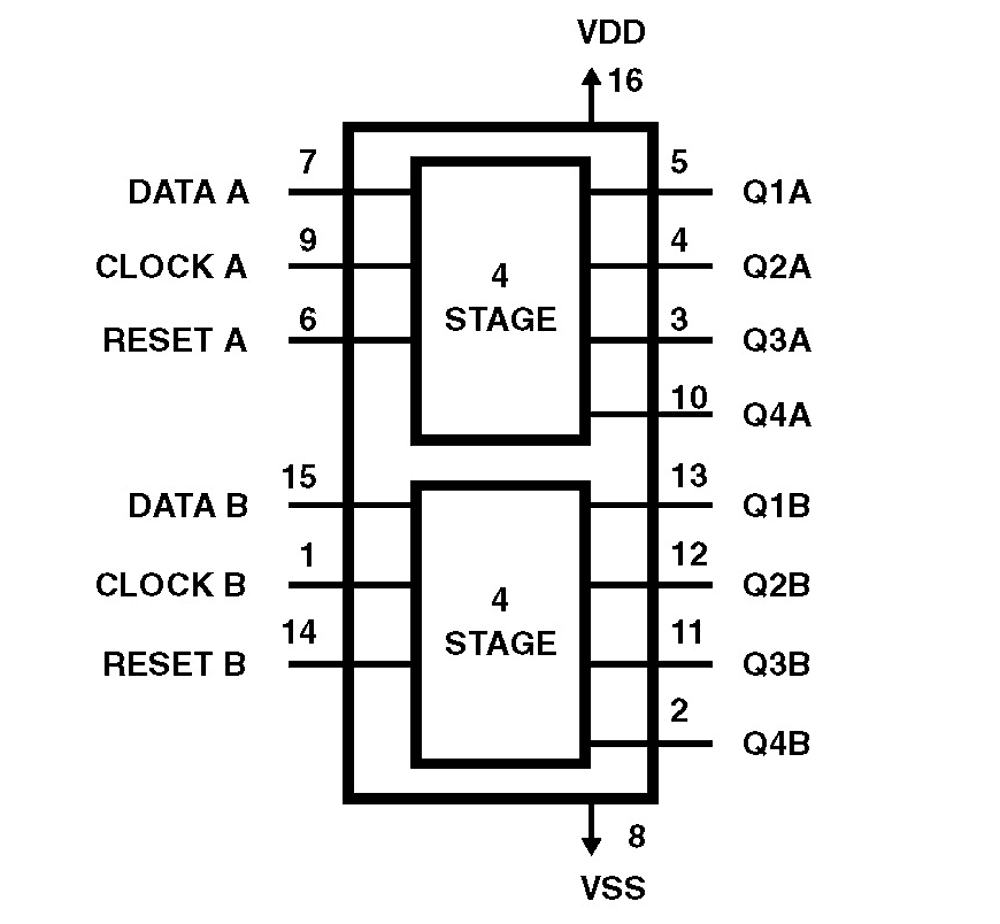

CD4015BMS consists of two identical, independent, 4-stage serial-input/parallel output registers. Each register has independent CLOCK and RESET inputs as well as a single serial DATA input. Q outputs are available from each of the four stages on both registers. All register stages are D type, master-slave flip-flops. The logic level present at the DATA input is transferred into the first register stage and shifted over one stage at each positive-going clock transition. Resetting of all stages is accomplished by a high level on the reset line. Register expansion to 8 stages using one CD4015BMS package, or to more than 8 stages using additional CD4015BMS's is possible. The CD4015BMS is supplied in these 16 lead outline packages: Braze Seal DIP H4X Frit Seal DIP H1F Ceramic Flatpack H6W