封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | DIE |

| Pkg. Code: | |

| Lead Count (#): | |

| Pkg. Dimensions (mm): | 0.0 x 0.0 x 0.00 |

| Pitch (mm): |

环境和出口类别

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pb (Lead) Free | Yes |

| RoHS (CD4029BHNSR) | 英语日文 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | DIE |

| Carrier Type | Die Waffle Pack |

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pkg. Dimensions (mm) | 0.0 x 0.0 x 0.00 |

| DLA SMD | 5962R9562102V9A |

| Pb (Lead) Free | Yes |

| Pb Free Category | None |

| MOQ | 100 |

| Temp. Range (°C) | -55 to +125°C |

| DSEE (MeV·cm2/mg) | 75 |

| Lead Compliant | No |

| Qualification Level | QML Class V (space) |

| Rating | Space |

| TID HDR (krad(Si)) | 100 |

| TID LDR (krad(Si)) | ELDRS free |

| Tape & Reel | No |

有关 CD4029BMS 的资源

描述

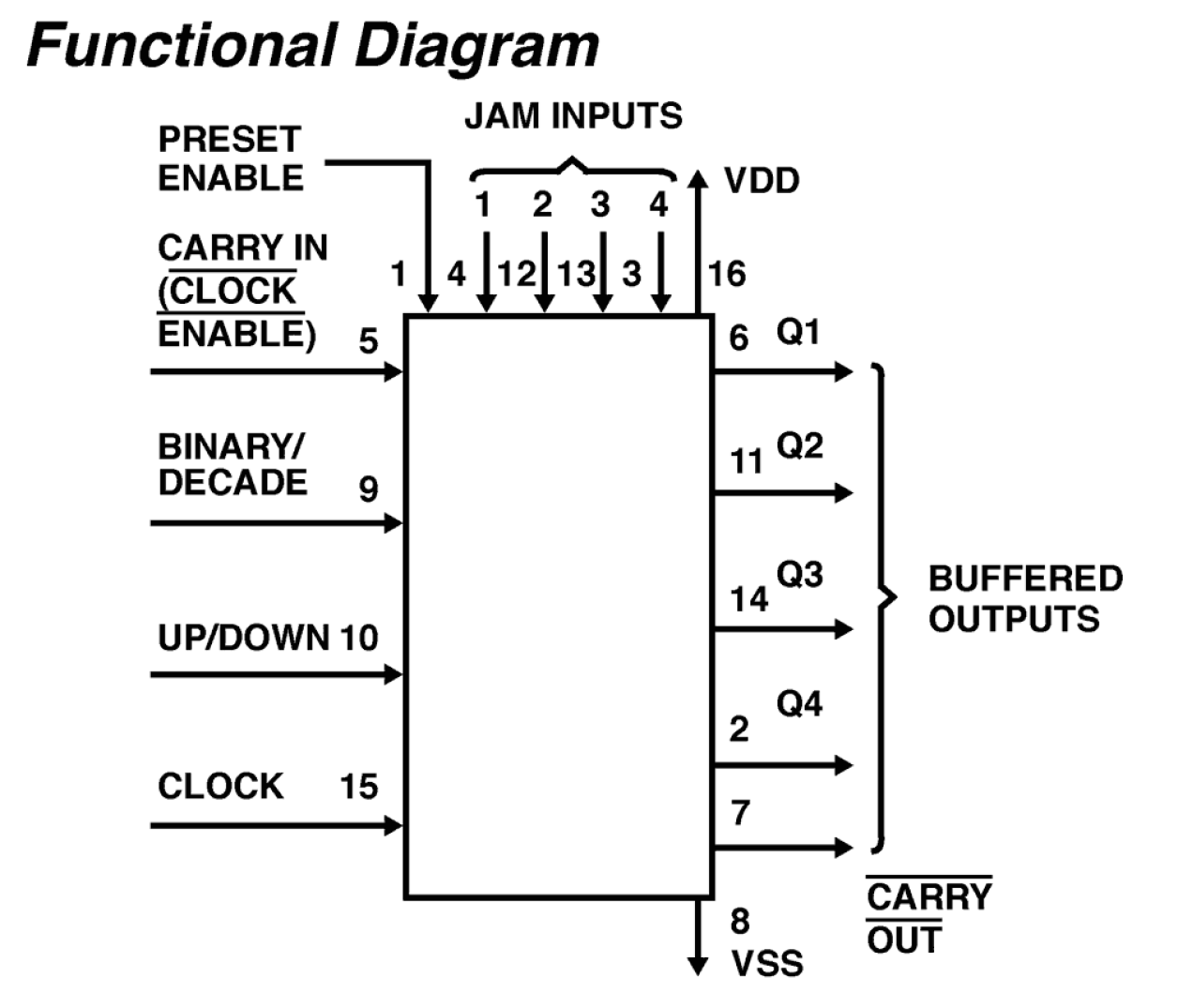

The CD4029BMS consists of a four-stage binary or BCD-decade up/down counter with provisions for look-ahead carry in both counting modes. The inputs consist of a single CLOCK, CARRY-IN (CLOCK ENABLE), BINARY/DECADE, UP/DOWN, PRESET ENABLE, and four individual JAM signals. Q1, Q2, Q3, Q4 and a CARRY-OUT OUT signal are provided as outputs. A high PRESET ENABLE signal allows information on the JAM INPUTS to preset the counter to any state asynchronously with the clock. A low on each JAM line, when the PRESET-ENABLE signal is high, resets the counter to its zero count. The counter is advanced one count at the positive transition of the clock when the CARRY-IN-IN and PRE-SET ENABLE signals are low. Advancement is inhibited when the CARRY-IN or PRESET ENABLE signals are high. The CARRY-OUT signal is normally high and goes low when the counter reaches its maximum count in the UP mode or the minimum count in the DOWN mode provided the CARRY-IN signal is low. The CARRY-IN signal in the low state can thus be considered a CLOCK ENABLE. The CARRY-IN terminal must be connected to VSS when not in use. Binary counting is accomplished when the BINARY/DECADE input is high; the counter counts in the decade mode when the BINARY/DECADE input is low. The counter counts up when the UP/DOWN input is high, and down when the UP/DOWN input is low. Multiple packages can be connected in either a parallel-clocking or a ripple-clocking arrangement. Parallel clocking provides synchronous control and hence faster response from all counting outputs. Ripple-clocking allows for longer clock input rise and fall times. The CD4029BMS is supplied in these 16-lead outline packages: Braze Seal DIP H4X, Frit Seal DIP H1F and Ceramic Flatpack H6W.