特性

- LP-HCSL outputs; save 8 resistors compared to standard HCSL outputs

- 45 mW typical power consumption in PLL mode; minimal power consumption

- OE# pins; support DIF power management

- HCSL-compatible differential input; can be driven by common clock sources

- LP-HCSL differential clock outputs; reduced power and board space

- Programmable slew rate for each output; allows tuning for various line lengths

- Programmable output amplitude; allows tuning for various application environments

- Pin/software selectable PLL bandwidth and PLL Bypass; minimize phase jitter for each application

- Outputs blocked until PLL is locked; clean system start-up

- Configuration can be accomplished with strapping pins; SMBus interface not required for device control

- 3.3 V tolerant SMBus interface works with legacy controllers

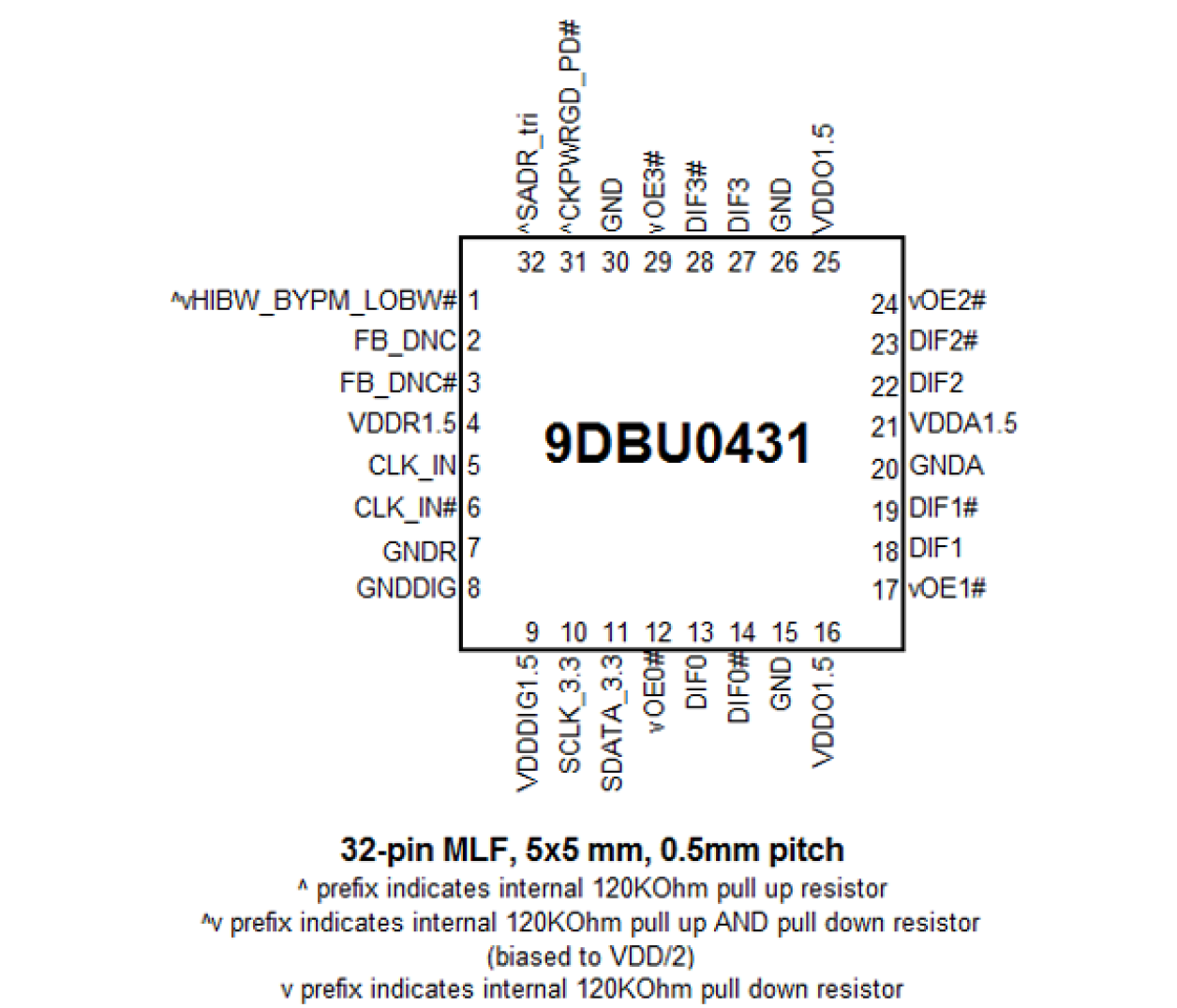

- Space-saving 32-pin 5x5mm VFQFPN; minimal board space

- 3 selectable SMBus addresses; multiple devices can easily share an SMBus segment

描述

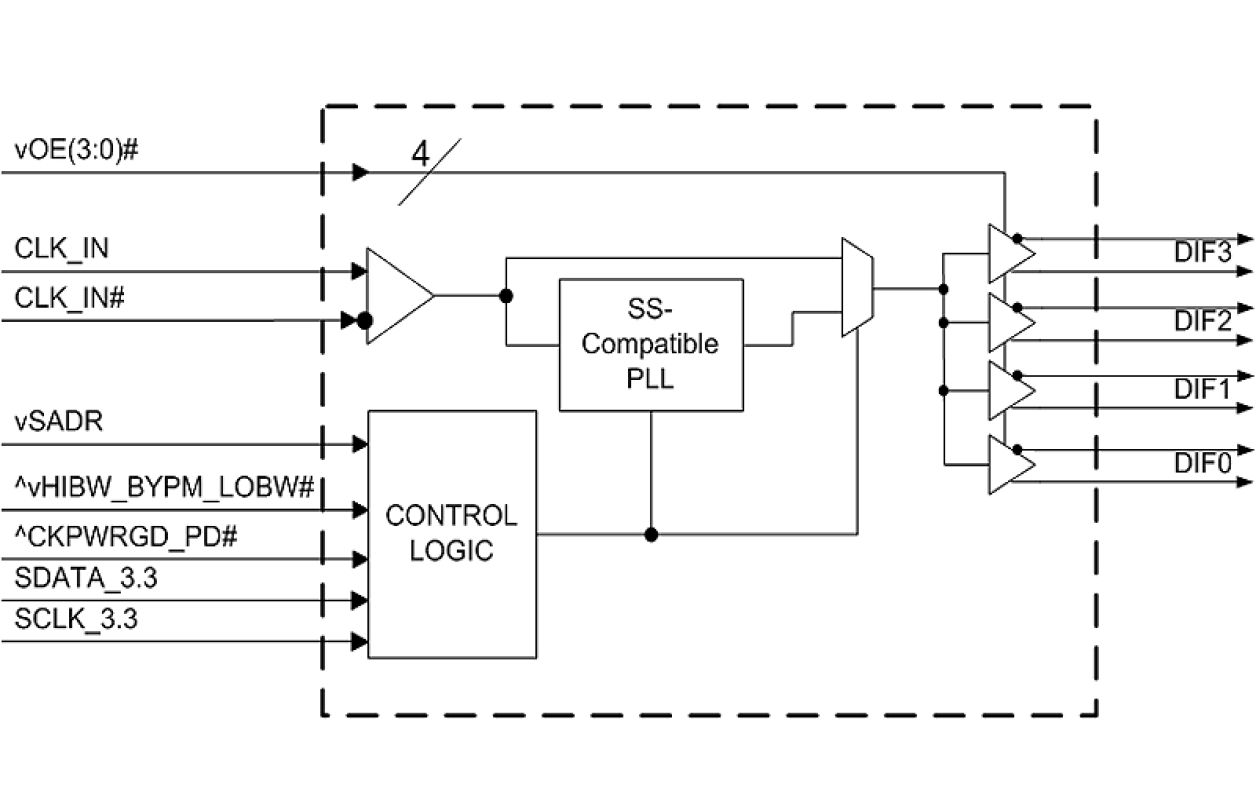

The 9DBU0431 is a member of IDT's 1.5 V Ultra-Low-Power (ULP) PCIe family. The device has 4 output enables for clock management, and 3 selectable SMBus addresses.

产品参数

| 属性 | 值 |

|---|---|

| Diff. Outputs | 4 |

| Diff. Output Signaling | LP-HCSL |

| Output Freq Range (MHz) | 1 - 167 |

| Diff. Inputs | 1 |

| Diff. Input Signaling | HCSL |

| Accepts Spread Spec Input | Yes |

| Power Consumption Typ (mW) | 45 |

| Supply Voltage (V) | 1.5 - 1.5 |

| Output Type | LP-HCSL |

| Package Area (mm²) | 25 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Input Freq (MHz) | 30 - 175 |

| Additive Phase Jitter Typ RMS (fs) | 313 |

| Function | Zero Delay Buffer |

| Input Type | HCSL |

| Output Banks (#) | 1 |

| Core Voltage (V) | 1.5 |

| Output Voltage (V) | 0.8 |

| Product Category | PCI Express Clocks |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 5.0 x 5.0 x 0.9 | 32 | 0.5 |

当前筛选条件