特性

- PCIe Gen1–4 compliant

- LP-HCSL outputs with integrated terminations; save 24 resistors compared to standard PCIe devices

- 54 mW typical power consumption; reduced thermal concerns

- Outputs can optionally be supplied from any voltage between 1.05 and 1.8V; maximum power savings

- OE# pins; support DIF power management

- Programmable slew rate for each output; allows tuning for various line lengths

- Programmable output amplitude; allows tuning for various application environments

- DIF outputs blocked until PLL is locked; clean system start-up

- Selectable 0%, -0.25% or -0.5% spread on DIF outputs; reduces EMI

- External 25 MHz crystal; supports tight ppm with 0 ppm synthesis error

- Configuration can be accomplished with strapping pins; SMBus interface not required for device control

- 3.3 V tolerant SMBus interface works with legacy controllers

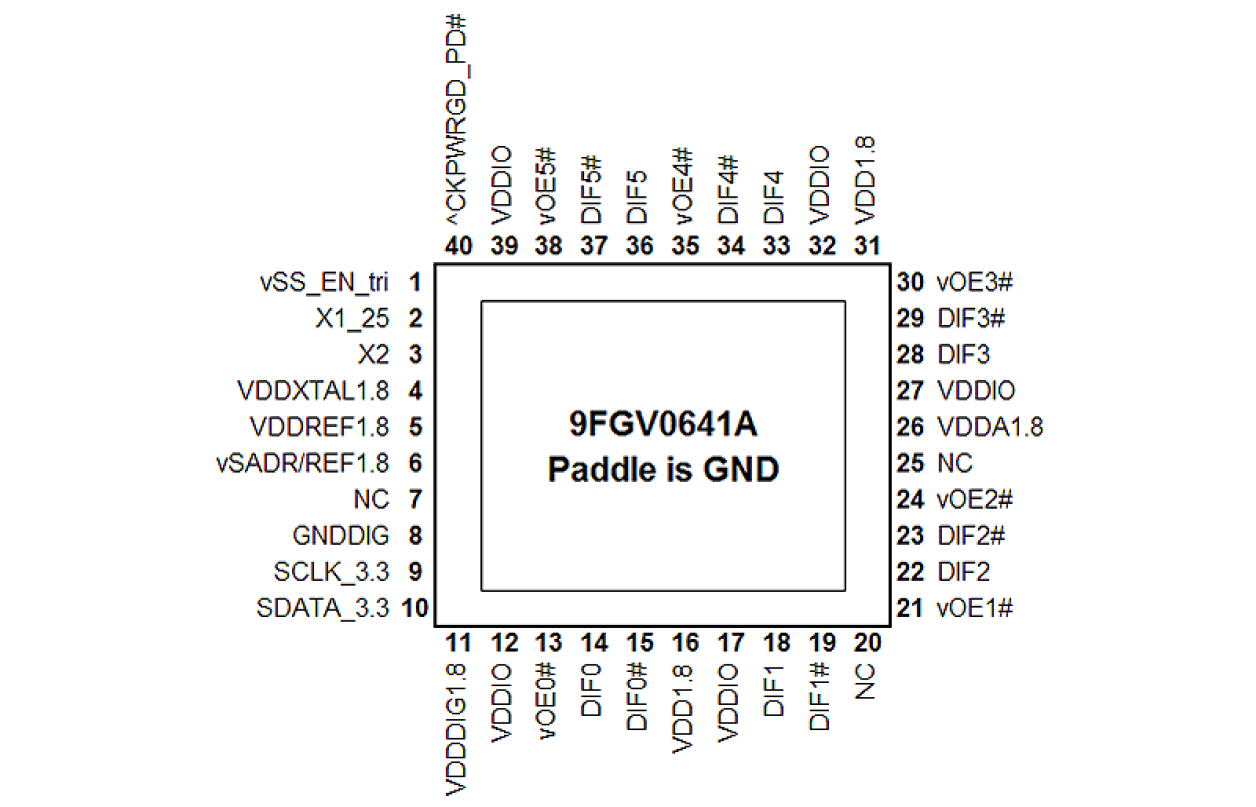

- Space saving 5x5 mm 40-pin VFQFPN; minimal board space

- Selectable SMBus addresses; multiple devices can easily share an SMBus segment

描述

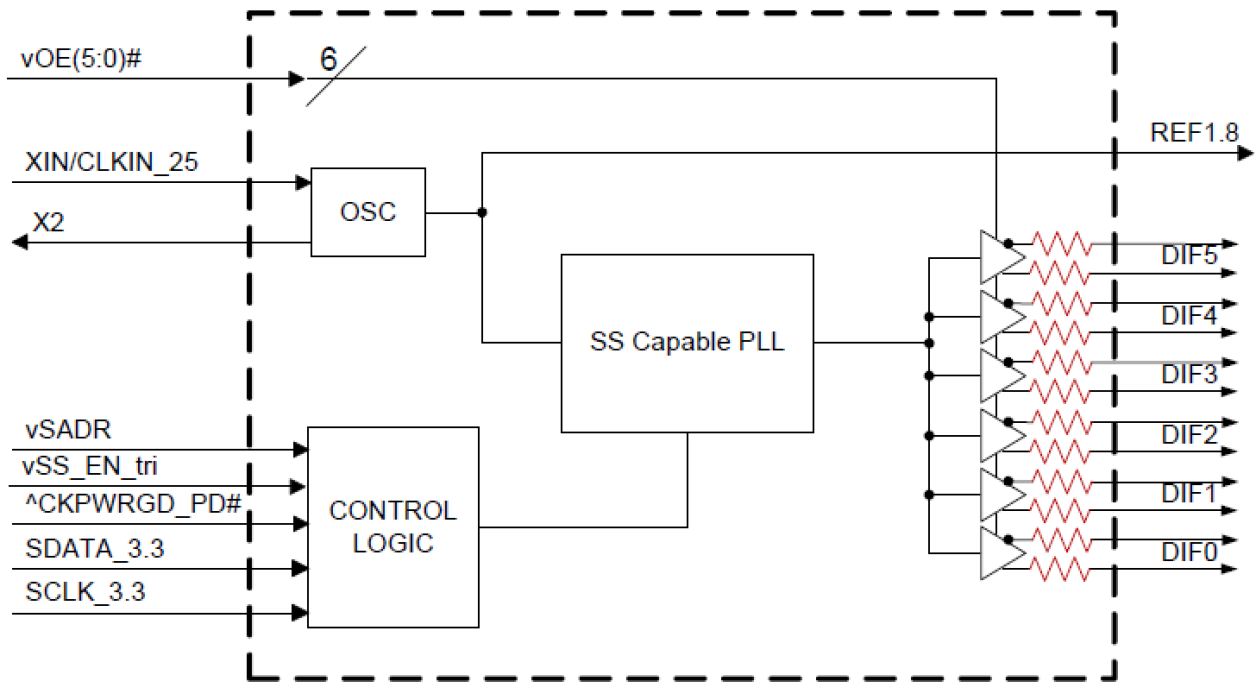

The 9FGV0641 is a member of IDT's SOC-Friendly 1.8V Very-Low-Power PCIe clock family. The device has integrated 100 ohm output terminations providing direction connection to 100 ohm transmission lines. The device also has 6 output enables for clock management and supports 2 different spread spectrum levels in addition to spread off.

For information regarding evaluation boards and material, please contact your local IDT sales representative.

产品参数

| 属性 | 值 |

|---|---|

| Temp. Range (°C) | -40 to 85°C, 0 to 70°C |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 5.0 x 5.0 x 0.9 | 40 | 0.4 |

应用方框图

| 具有 AI 功能的可扩展人机界面 SMARC SoM 可扩展的 SoM,具有多核处理、高级图形和强大的连接性,适用于智能人机界面(HMI)。 |

| 高性能人机界面(HMI)系统 多功能模块系统(SoM),用于驱动各种人机界面功能。 |

| 多显示器 HMI SoM 具有优化功耗和时序的 SOM 支持多显示器嵌入式应用。 |

当前筛选条件

筛选

软件与工具

样例程序

模拟模型

Ron Wade, chief PCIe system architect explains the fundamental difference in reference clock jitter budgets between the first three generations of the specification and those of Gen4 and Gen5 which raise new challenges for designers.

Related Resources

This whiteboard video presents a brief overview comparing the evolution of PCI Express data rates through five generations versus that of the common clock jitter specifications.

Renesas's chief PCIe system architect explains how to derive separate reference clock jitter limits from the PCI Express Gen4 and Gen5 specifications.

A detailed overview of IDT's full-featured PCI Express (PCIe) clock and timing solutions. The presentation addresses PCIe Gen 1, Gen 2, Gen 3, and Gen 4 architectures and how IDT's industry-leading solutions provide all the functions, features, and performance required by the application.

Presented by Ron Wade, System Architect at IDT. For more information visit the PCIe clocks page.

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

In this episode, Ron Wade from IDT (acquired by Renesas) explains PCIe common clocking and its impact on timing solutions. Learn about using a single clock source, fan-out buffers, and the considerations for spread spectrum and non-spread spectrum clocking in PCIe systems.

In this video, we explore PCIe with separate reference clocks and the effects of clock selection. Learn how separate reference clocks work and their impact on system performance and stability.

This video provides a high-level overview of Separate Reference Clock with Independent Spread (SRIS) architectures for PCI Express systems, additional performance requirements that this clocking architecture imposes on the reference clocks, and some system implications encountered trying to implement the architecture.

IDT provides a brief overview of the timing solutions optimized for various configurations using the NXP (Freescale) QorIQ / Layerscape processors.

Resources

IDT provides a brief tutorial on the timing solutions required for NXP (Freescale) QorIQ / Layerscape processor-based systems.

Presented by Ron Wade, PCI Express timing expert.

IDT (acquired by Renesas) engineer provides a brief tutorial describing the main differences between standard HCSL and low-power HCSL (LP-HCSL).

Presented by Ron Wade, PCI Express timing expert.

Related Resources

An overview of IDT's full-featured PCI Express (PCIe) clock generators addressing PCIe Gen 1, Gen 2, Gen 3, and Gen 4.

Presented by Ron Wade, System Architect at IDT.

An overview of PCI Express applications and how IDT's industry-leading portfolio of PCIe clock products addresses the requirements. The video briefly discusses PCIe riser cards, embedded SOC, and PCIe storage (NVME) examples.

Presented by Ron Wade, System Architect at IDT.

A brief overview of how data rates have changed from PCI Express (PCIe) Generation 1, Gen 2, Gen 3, Gen 4 and Gen 5.

Presented by Ron Wade, system architect at IDT. For more information about IDT's PCIe timing solutions, visit the PCI Express (PCIe) Clocks page.

A brief overview of how clock and timing specifications have changed from PCI Express (PCIe) Generation 1, Gen 2, Gen 3, Gen 4 and Gen 5.

Presented by Ron Wade, system architect at IDT (acquired by Renesas). For more information, visit Renesas's PCIe Timing Solutions page.

A brief overview of the PCI Express common clock (CC) jitter model, and the transfer functions as they relate to the timing PLLs. This model applies to PCI Express (PCIe) Gen 2, Gen 3, Gen 4 and Gen 5. The equations would be slightly different for other PCIe architectures, such as SRIS, SRnS, or data clocked.

Presented by Ron Wade, system architect at IDT (acquired by Renesas). For more information about Renesas's PCIe timing solutions, visit the PCI Express (PCIe) Clocks page.