概览

描述

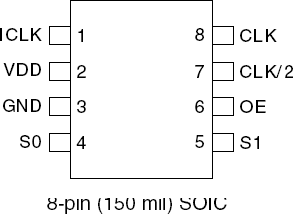

The 542 is cost effective way to produce a high-quality clock output divided from a clock input. The chip accepts a clock input up to 156 MHz at 3.3 V and produces a divide by 2, 4, 6, 8, 12, or 16 of the input clock. There are two outputs on the chip, one being a low-skew divide by two of the other. For instance, if an 100 MHz input clock is used, the 542 can produce low-skew 50 MHz and 25 MHz clocks, or low skew 25 MHz and 12.5 MHz clocks. The chip has an all-chip power-down mode that stops the outputs low, and an OE pin that tri-states the outputs. See the 501, 502, 511, 512, and 525 for clock multipliers.

特性

- 8-pin SOIC package, Pb free

- Available in RoHS compliant package

- IDT's lowest cost clock divider

- Low skew (500 ps) outputs. One is /2 of the other

- Easy to use with other generators and buffers

- Input clock frequency up to 156 MHz

- Output clock duty cycle of 45/55

- Power-down turns off chip

- Output Enable

- Advanced, low-power CMOS process

- Operating voltage of 3.3 V or 5 V

- Does not degrade phase noise - no PLL

- Available in industrial and commercial temperature ranges

产品对比

应用

设计和开发

产品选项

当前筛选条件