概览

描述

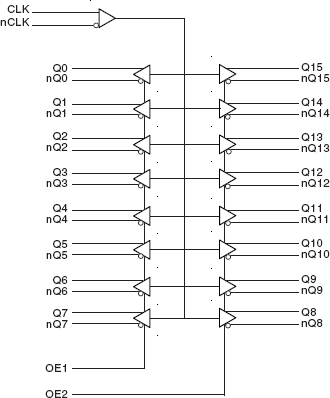

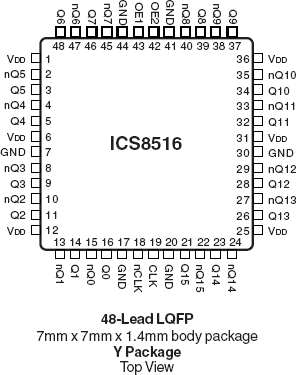

The 8516 is a low skew, high performance 1-to-16 Differential-to-LVDS Clock Distribution Chip. The 8516 CLK, nCLK pair can accept any differential input levels and translates them to 3.3V LVDS output levels. Utilizing Low Voltage Differential Signaling (LVDS), the 8516 provides a low power, low noise, pointto- point solution for distributing clock signals over controlled impedances of 100?. Dual output enable inputs allow the 8516 to be used in a 1-to-16 or 1-to-8 input/output mode. Guaranteed output and part-to-part skew specifications make the 8516 ideal for those applications demanding well defined performance and repeatability.

特性

- Sixteen differential LVDS outputs

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

- Maximum output frequency: 700MHz

- Translates any differential input signal (LVPECL, LVHSTL, SSTL, DCM) to LVDS levels without external bias networks

- Translates any single-ended input signal to LVDS with resistor bias on nCLK input

- Multiple output enable inputs for disabling unused outputs in reduced fanout applications

- LVDS compatible

- Output skew: 90ps (maximum)

- Part-to-part skew: 500ps (maximum)

- Propagation delay: 2.4ns (maximum)

- Additive phase jitter, RMS: 148fs (typical)

- 3.3V operating supply

- 0°C to 70°C ambient operating temperature

- Available in lead-free RoHS compliant package

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件