概览

描述

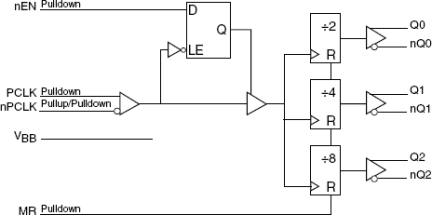

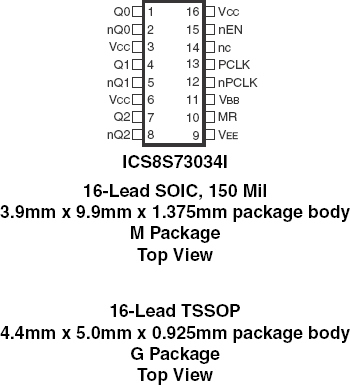

The 8S73034I is a high-speed, differential-to- LVPECL clock divider designed for high-performance telecommunication, computing and networking applications. High clock frequency capability and the differential design make the 8S73034I an ideal choice for performance clock distribution networks. The device frequency-divides the input clock by ÷2, ÷4 and ÷8. Each frequency-divided clock signal is output at a separate LVPECL output. The differential input pair can be driven by LVPECL, LVDS, CML and SSTL signals. Single-ended input signals are supported by using the integrated bias voltage generator (VBB). The 8S73034I is optimized for 3.3V and 2.5V power supply voltages and the temperature range of -40 to +85°C. The device is available in space-saving 16-lead TSSOP and SOIC packages.

特性

- ÷2, ÷4 and ÷8 clock frequency divider

- Three differential LVPECL output pairs

- One differential PCLK, nPCLK input pair

- PCLK, nPCLK pair can accept the following differential input levels: LVPECL, LVDS, CML

- VBB bias voltage generator supports single-ended LVPECL clock input signals

- LVCMOS control inputs

- Maximum input frequency: 3.2GHz

- Translates any single-ended input signal to 3.3V LVPECL levels with bias resistors on nPCLK input

- LVPECL mode operating voltage supply range: VCC = 2.375V to 3.8V, VEE = 0V

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

产品对比

应用

设计和开发

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件