特性

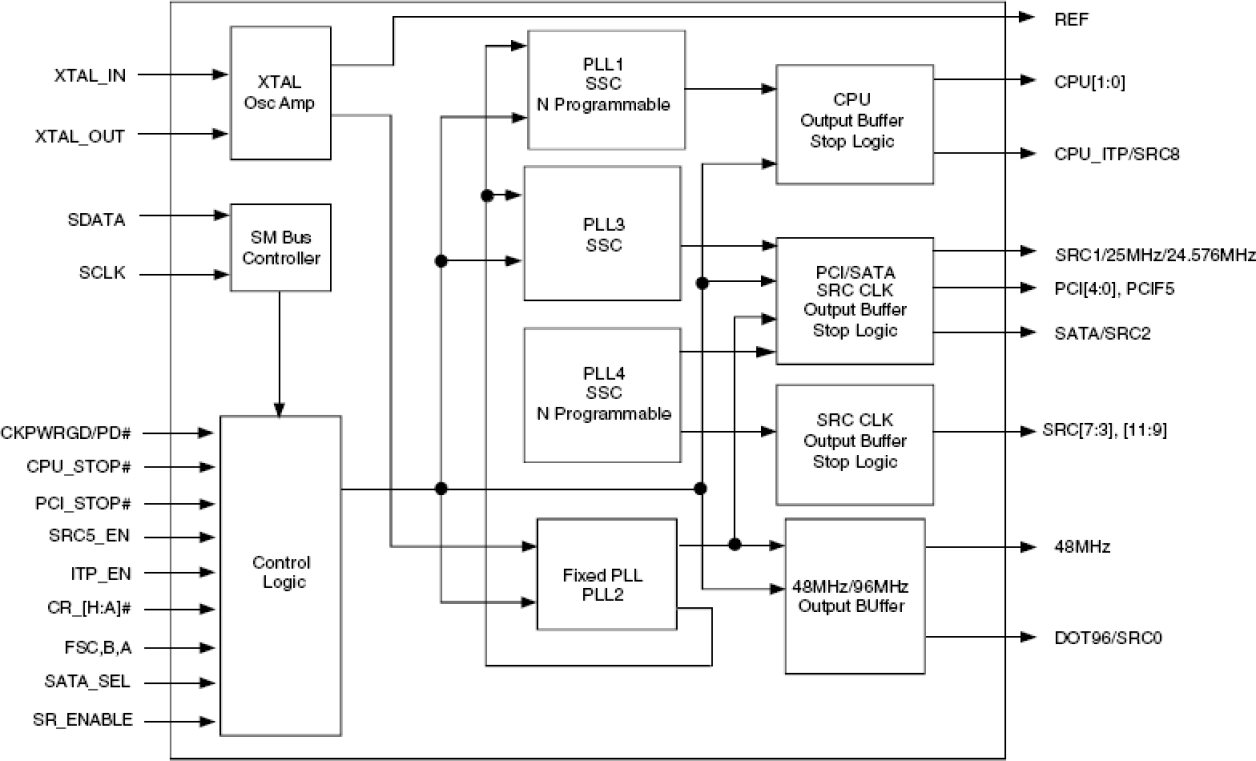

- Compliant with Intel CK505 Gen II spec

- One high precision PLL for CPU, SSC and N programming

- One high precision PLL for SRC, SSC and N programming

- One high precision PLL for SATA/PCI, and SSC

- One high precision PLL for 96MHz/48MHz

- Push-pull IOs for differential outputs

- Support spread spectrum modulation, -0.5 down spread and others

- Support SMBus block read/write, byte read/write

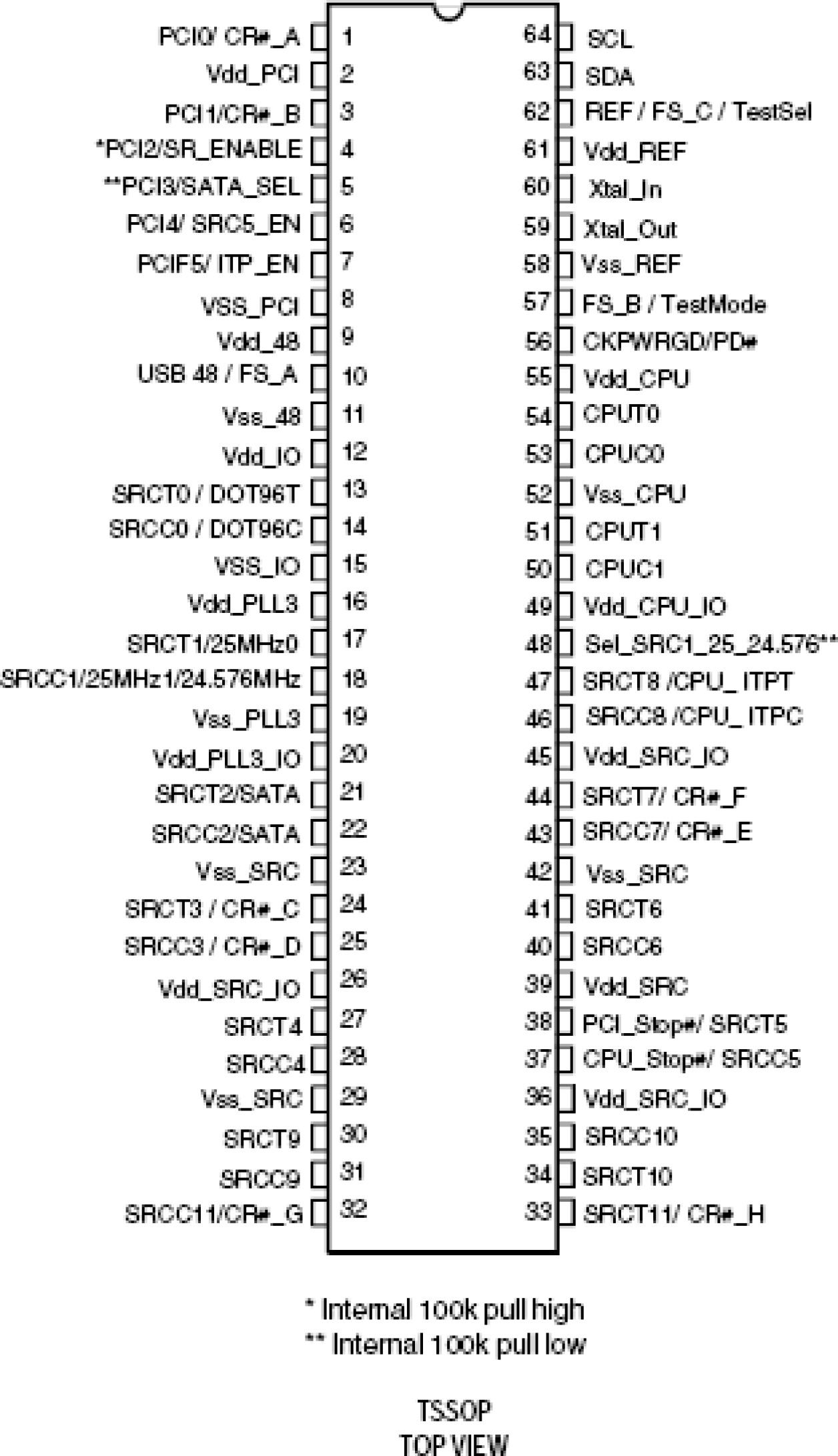

- Available in TSSOP package

- 2 - 0.7V differential CPU CLK pair

- 10 - 0.7V differential SRC CLK pair

- 1 - CPU_ITP/SRC differential clock pair

- 1 - SRC0/DOT96 differential clock pair

- 6 - PCI, 33.3MHz

- 1 - 48MHz

- 1 - REF

- 1 - SATA

- Direct CPU and SRC clock frequency programming—write the Hex number into Byte [16:18], 1MHz stepping.

- Linear and smooth transition for the CPU and SRC frequency programming.

- SATA PLL source hardware select latch pin, PLL2 or PLL4.

- Internal serial resistor hardware enable latch pin.

- WOL 25MHz support.

描述

PROGRAMMABLE FLEXPC LP/S CLOCK FOR INTEL BASED SYSTEMS

当前筛选条件