封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | DIE |

| Pkg. Code: | |

| Lead Count (#): | |

| Pkg. Dimensions (mm): | 0.0 x 0.0 x 0.00 |

| Pitch (mm): |

环境和出口类别

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pb (Lead) Free | Yes |

| ECCN (US) | 9A515.e.1 |

| HTS (US) | 8542.39.0090 |

| RoHS (HCS109HMSR) | 英语日文 |

产品属性

| Pkg. Type | DIE |

| Carrier Type | Die Waffle Pack |

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pkg. Dimensions (mm) | 0.0 x 0.0 x 0.00 |

| DLA SMD | 5962R9578401V9A |

| Pb (Lead) Free | Yes |

| Pb Free Category | None |

| MOQ | 100 |

| Temp. Range (°C) | -55 to +125°C |

| DSEE (MeV·cm2/mg) | SEL free |

| Lead Compliant | No |

| Qualification Level | QML Class V (space) |

| Rating | Space |

| TID HDR (krad(Si)) | 200 |

| TID LDR (krad(Si)) | ELDRS free |

| Tape & Reel | No |

有关 HCS109MS 的资源

描述

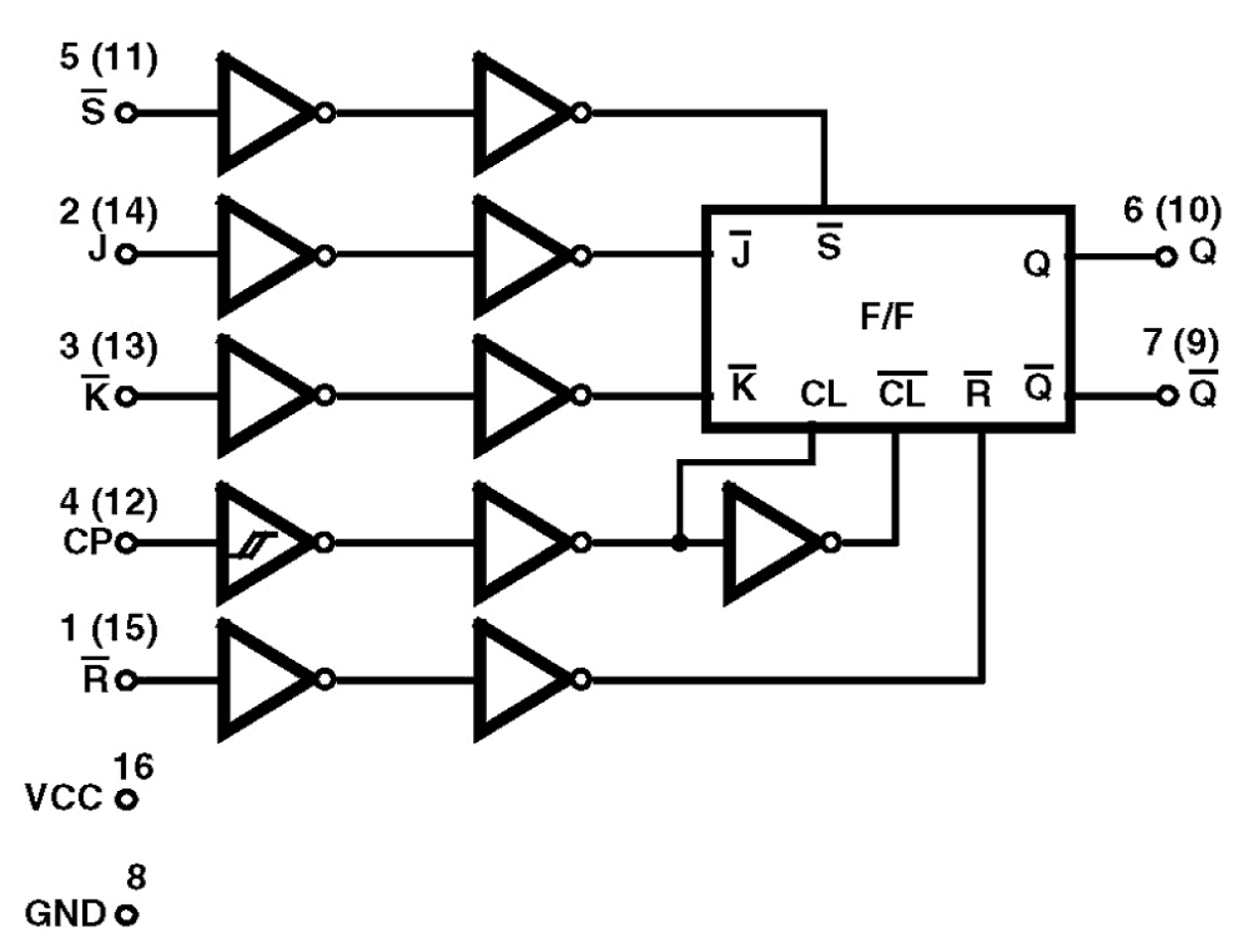

The Intersil HCS109MS is a radiation hardened dual J-K flip-flop with Set and Reset. The flip-flop changes state with the positive transition of the clock. The HCS109MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of the radiation hardened, high-speed, CMOS/SOS logic family. The HCS109MS is supplied in a 16-lead Ceramic Flatpack (K suffix) or an SBDIP package (D suffix).