封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | LQFP |

| Pkg. Code: | QMB |

| Lead Count (#): | 48 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 0.00 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | |

| Pb (Lead) Free | No |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | LQFP |

| Carrier Type | Tray |

| Filter Subtype | DDS |

| Filtering | None |

| Frequency Resolution | 48 |

| Input Data (Bits) | 14 |

| Input Rate (MSPS) | 125 |

| Lead Count (#) | 48 |

| Length (mm) | 7 |

| MOQ | 250 |

| Modulation Formats | QPSK, FSK |

| Output | Analog |

| Pb (Lead) Free | No |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 0.00 |

| Qualification Level | Standard |

| Temp. Range (°C) | -40 to +85°C |

| Width (mm) | 7 |

有关 ISL5314 的资源

描述

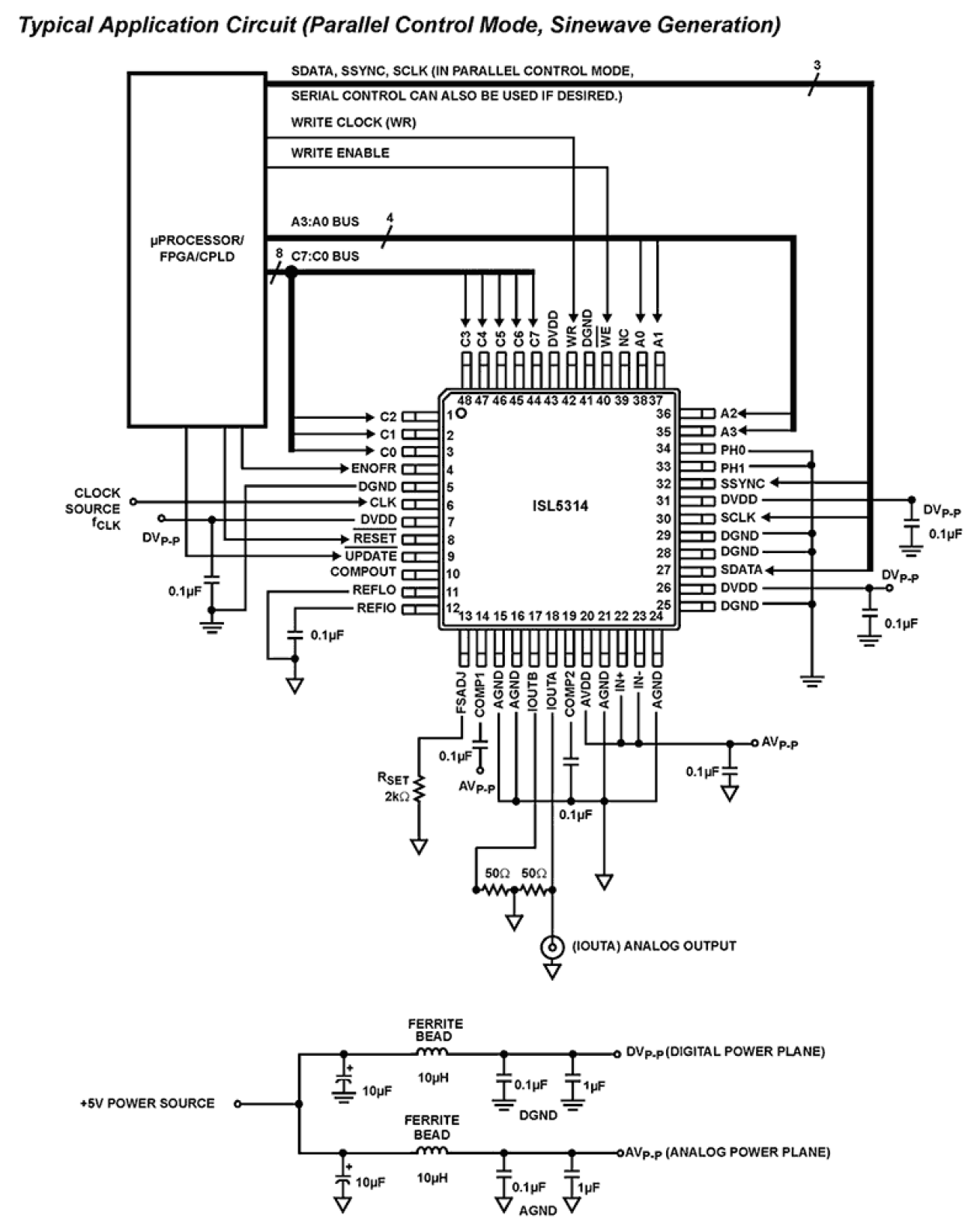

The 14-bit ISL5314 is a complete direct digital synthesizer (DDS) system in a single 48 Ld LQFP package. A 48-bit programmable carrier NCO (numerically controlled oscillator) and a high-speed 14-bit digital-to-analog converter (DAC) are integrated into a stand-alone DDS. The DDS accepts 48-bit center and offset frequency control information via a parallel processor interface. A 40-bit frequency tuning word can also be loaded via an asynchronous serial interface. Modulation control is provided by 3 external pins. The PH0 and PH1 pins select phase offsets of 0°, 90°, 180°, and 270°, while the ENOFR pin enables or zeros the offset frequency word to the phase accumulator. The parallel processor interface has an 8-bit write-only data input C(7:0), a 4-bit address A(3:0) bus, a Write Strobe (WR), and a Write Enable. The processor can update all registers simultaneously by loading a set of master registers, then transfer all master registers to the slave registers by asserting the UPDATE pin.