特性

- Integrated SAW delay line

- Output of 62.5 to 175 MHz

- Low phase jitter < 0.5 ps RMS typical (12kHz to 20MHz or 50kHz to 80MHz)

- Pin-selectable PLL divider ratios support FEC ratios

- M1060/65: OTU1 (255/238) and OTU2 (255/237) mapping

- M1061/66: OTU1 (238/255) or OTU2 (237/255) de-mapping

- M1062/67: OTU1 (238/255) and OTU2 (237/255) de-mapping

- LVPECL clock output

- Reference clock inputs support differential LVDS, LVPECL, as well as single-ended LVCMOS, LVTTL

- Loss of Lock (LOL) output pin

- Narrow bandwidth control input (NBW pin) to adjust loop bandwidth

- Hitless Switching (HS) options with or without Phase Build-out (PBO) are available to enable SONET (GR-253)/SDH (G.813) MTIE and TDEV compliance during reference clock reselection

- Single 3.3V power supply

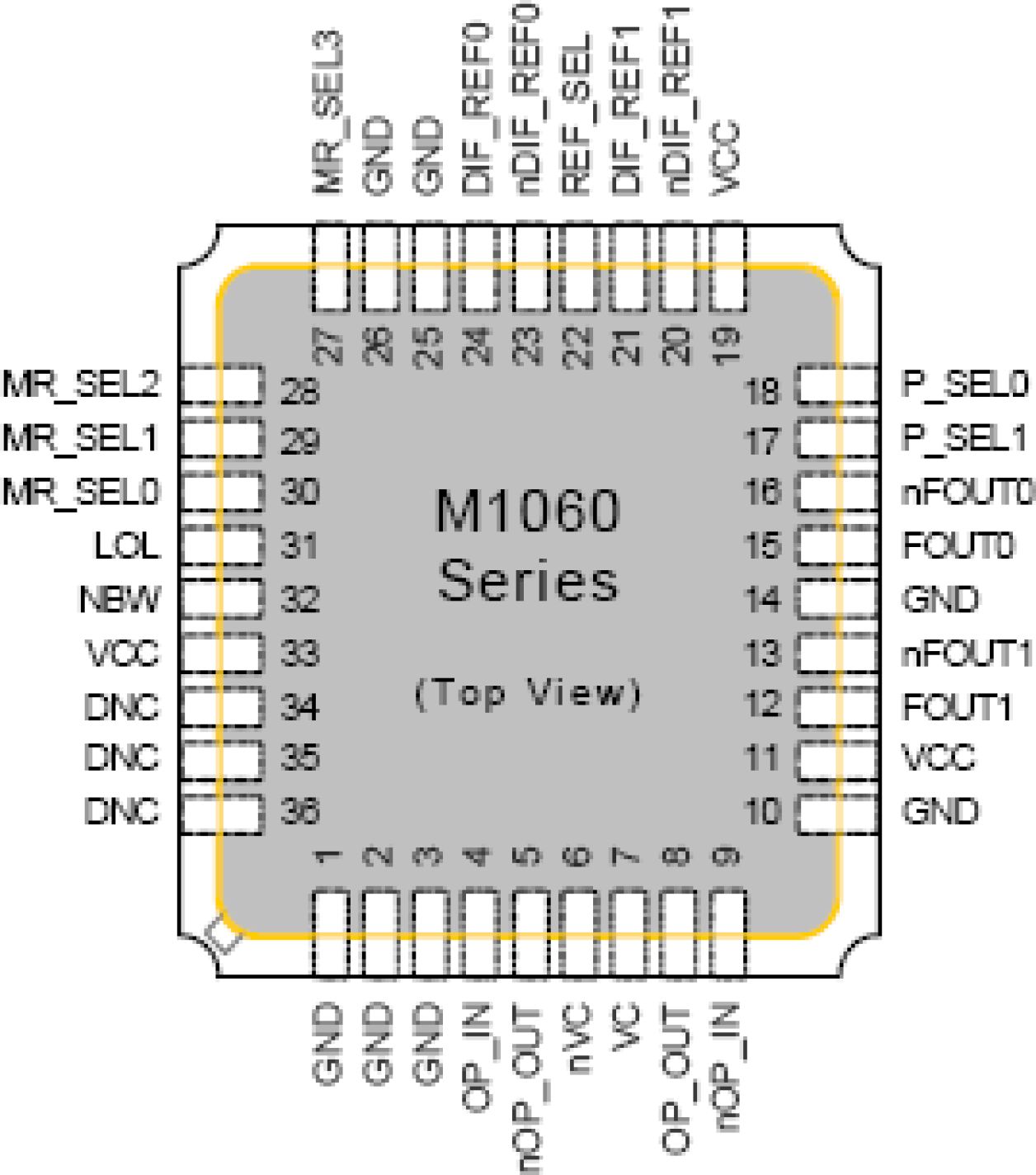

- Small 9mm x 9mm SMT (surface mount) package

描述

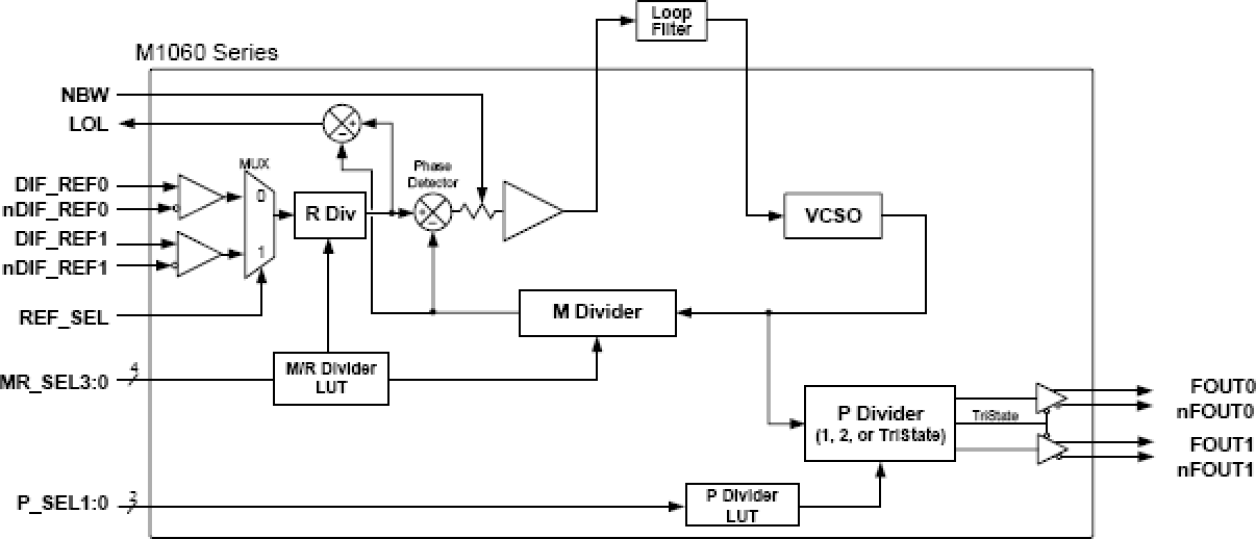

The M106x Voltage Controlled SAW Oscillator (VCSO) based clock PLLs are designed for Forward Error Correction (FEC) clock ratio translation in 10Gb optical systems such as OC-192 or 10GbE. They support FEC clock multiplication ratios, both forward (mapping) and inverse (de-mapping). Multiplication ratios are pin-selected from pre-programming look-up tables.

当前筛选条件