特性

- Integrated SAW (surface acoustic wave) delay line

- VCSO center frequency of 491.52MHz

- Jitter 9ps rms, typical, over 100Hz to 12kHz Jitter 3ps rms, typical, over 12kHz to 1GHz

- PLL phase slope limiter circuit

- Single-ended reference inputs support LVCMOS, LVTTL

- All output clocks are differential LVPECL compatible

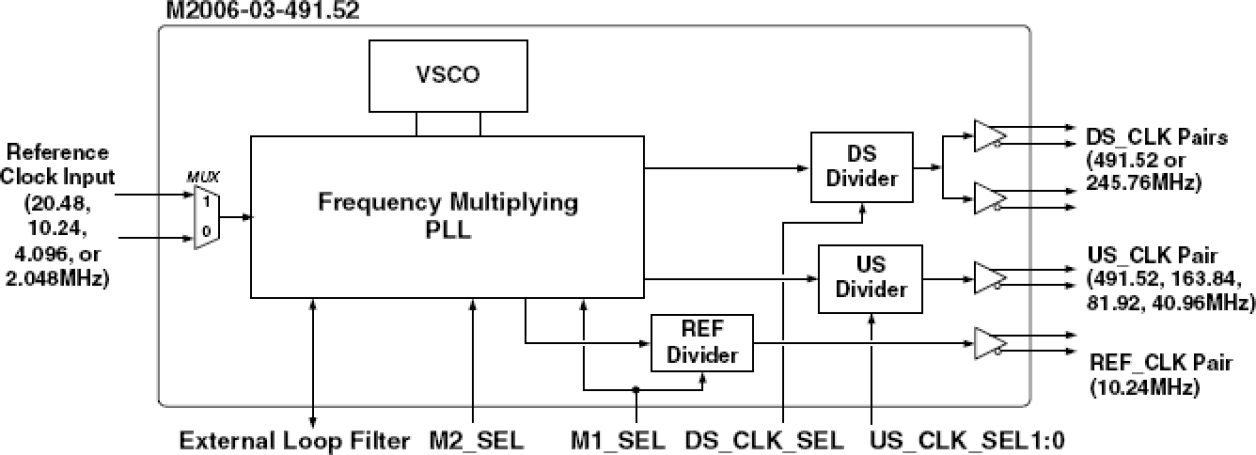

- Two downstream clocks, frequency-selectable

- One upstream clock, frequency-selectable

- REF_OUT always provides a 10.24MHz reference clock

- All output rising edges aligned to within 1nsec of selected input reference rising edge (unless M2_SEL= 1)

- Output duty cycle 47-53% worse case

- Single 3.3V power supply

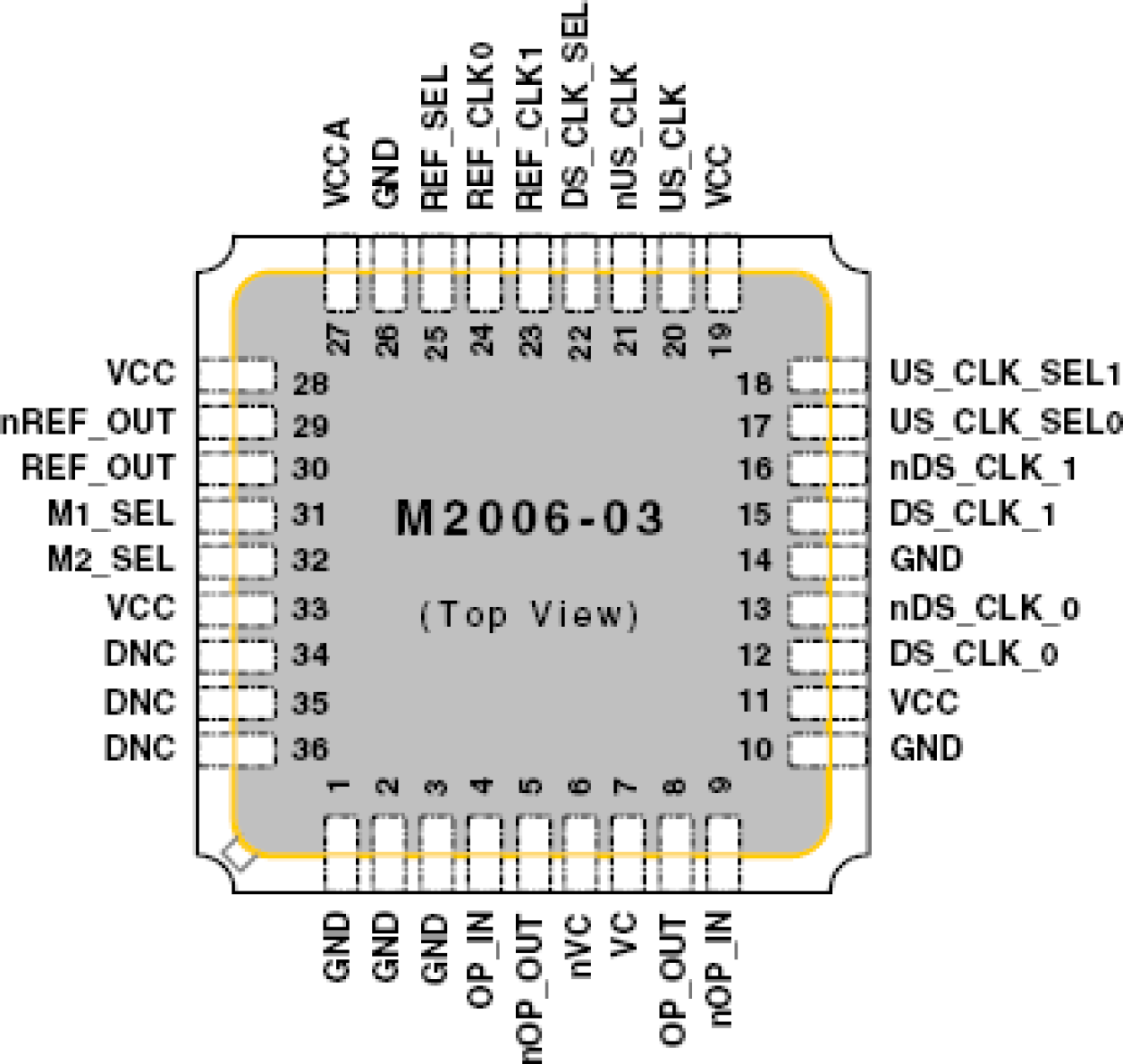

- Small 9 x 9 mm SMT (surface mount) package

描述

The M2006-03 is a VCSO (Voltage Controlled SAW Oscillator) based clock generator PLL designed for frequency translation and jitter attenuation of a master reference clock in a cable modem termination system (CMTS). External loop filter components allow tailoring of the PLL loop response. The M2006-03 includes a phase-slope limiting feature to prevent disruptive output clock phase changes upon input reference reselection.

当前筛选条件