封装信息

| CAD 模型: | View CAD Model |

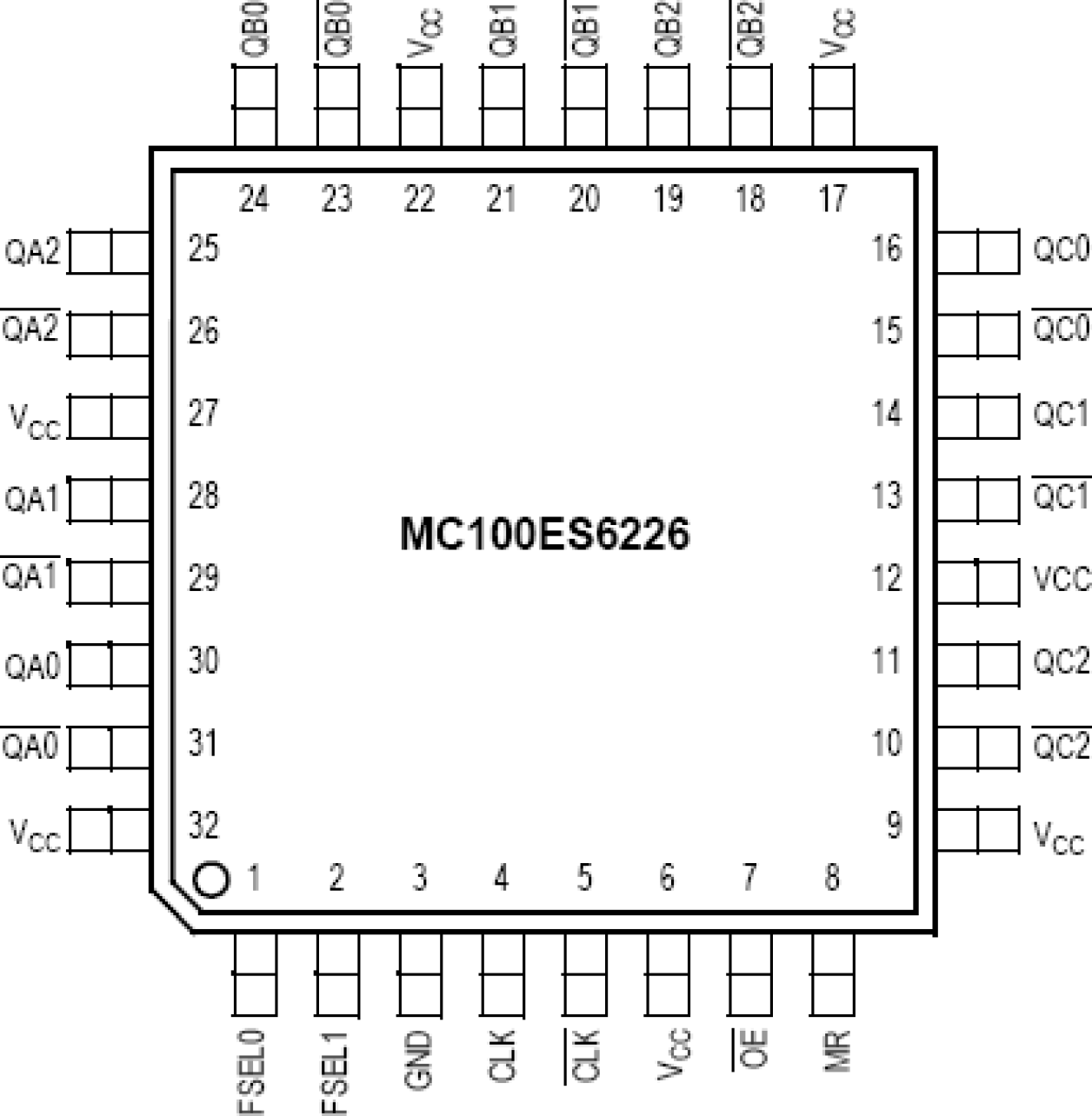

| Pkg. Type: | TQFP |

| Pkg. Code: | PRG32 |

| Lead Count (#): | 32 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.8 |

环境和出口类别

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

| Moisture Sensitivity Level (MSL) | 3 |

产品属性

| Pkg. Type | TQFP |

| Lead Count (#) | 32 |

| Pb (Lead) Free | Yes |

| Carrier Type | Reel |

| Core Voltage (V) | 2.5V, 3.3V |

| Divider Value | 1, 2 |

| Function | Buffer, Divider |

| Input Freq (MHz) | 3000 |

| Input Type | LVPECL |

| Inputs (#) | 1 |

| Length (mm) | 7 |

| MOQ | 2000 |

| Moisture Sensitivity Level (MSL) | 3 |

| Output Banks (#) | 3 |

| Output Freq Range (MHz) | 3000 |

| Output Skew (ps) | 20 |

| Output Type | LVPECL |

| Output Voltage (V) | 2.5V, 3.3V |

| Outputs (#) | 9 |

| Package Area (mm²) | 49 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Qty. per Carrier (#) | 0 |

| Qty. per Reel (#) | 2000 |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 7 |

有关 MC100ES6226 的资源

描述

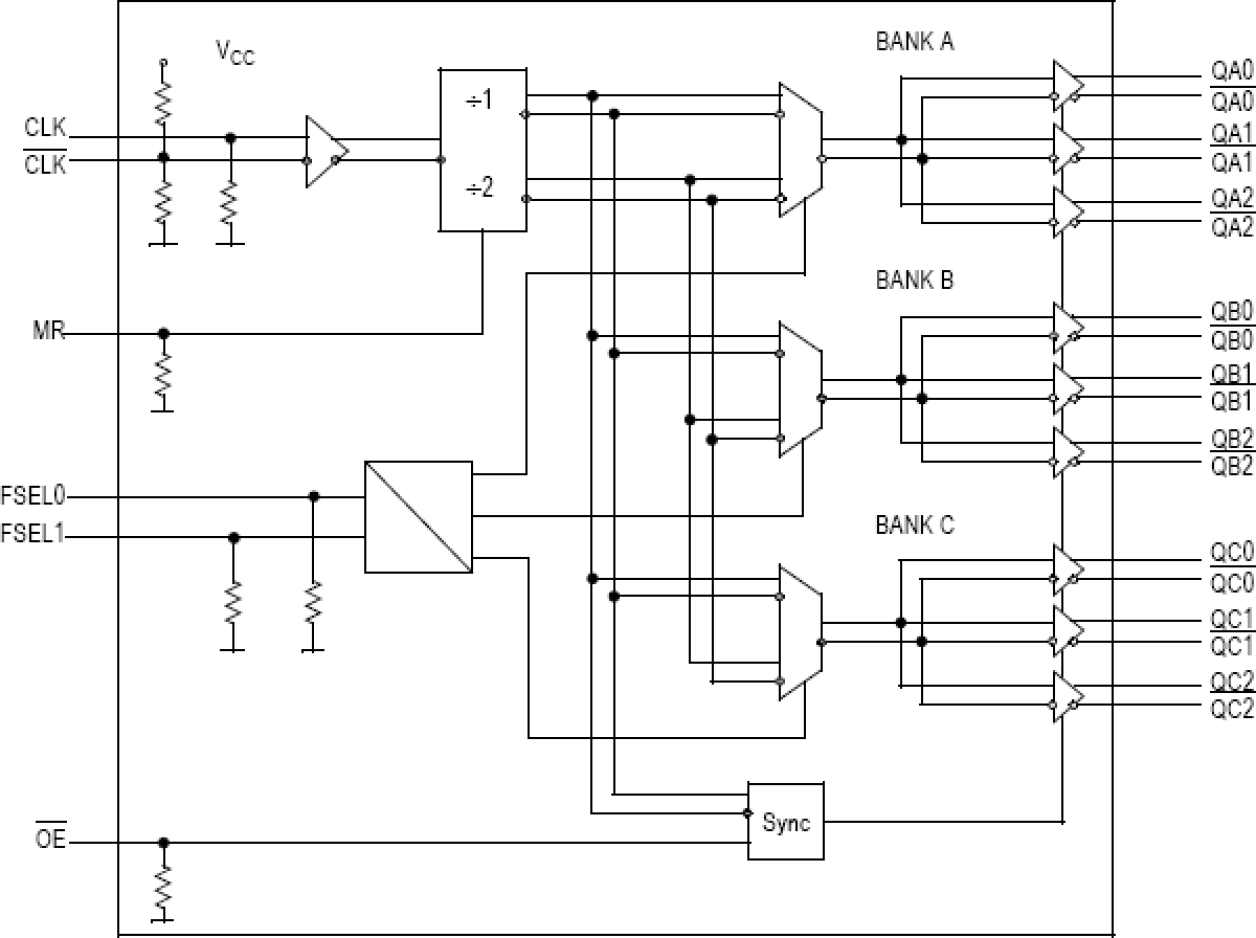

MC100ES6226 is designed for very skew critical differential clock distribution systems and supports clock frequencies from DC up to 3.0 GHz. Typical applications for the MC100ES6226 are primary clock distribution systems on backplanes of high-performance computer, networking and telecommunication systems, as well as on-board clocking of OC-3, OC-12 and OC-48 speed communication systems. The MC100ES6226 can be operated from a 3.3 V or 2.5 V positive supply without the requirement of a negative supply line. Each of the output banks of three differential clock output pairs may be independently configured to distribute the input frequency or half of the input frequency. The FSEL0 and FSEL1 clock frequency selects are asynchronous control inputs. Any changes of the control inputs require a MR pulse for resynchronization of the ÷2 outputs.