封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TSSOP |

| Pkg. Code: | PAG56 |

| Lead Count (#): | 56 |

| Pkg. Dimensions (mm): | 14.0 x 6.1 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 56 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 34 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Abs. Pull Range Min. (± PPM) | 115 |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 0.002 - 170 |

| Input Type | LVCMOS |

| Inputs (#) | 1 |

| Length (mm) | 14 |

| MOQ | 68 |

| Output Banks (#) | 3 |

| Output Freq Range (MHz) | 0.5 - 160 |

| Output Type | LVCMOS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 3 |

| Package Area (mm²) | 85.4 |

| Phase Jitter Typ RMS (ps) | 80 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 14.0 x 6.1 x 1.0 |

| Pkg. Type | TSSOP |

| Product Category | Jitter Attenuators |

| Prog. Clock | No |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | No |

| Thickness (mm) | 1 |

| Width (mm) | 6.1 |

| 已发布 | No |

有关 MK2069-04 的资源

描述

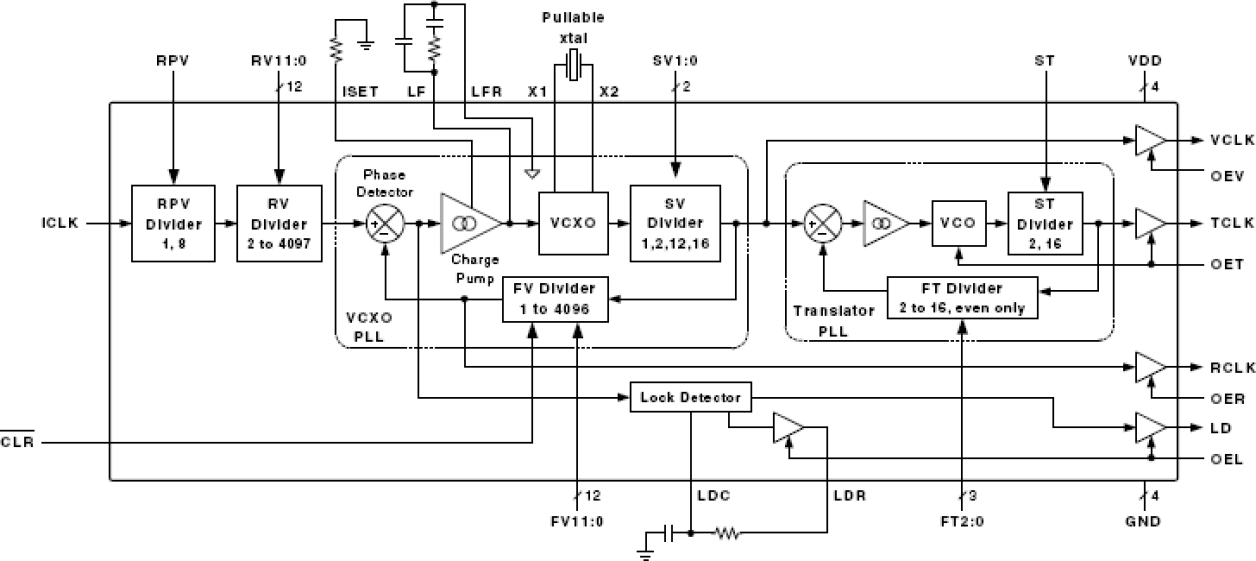

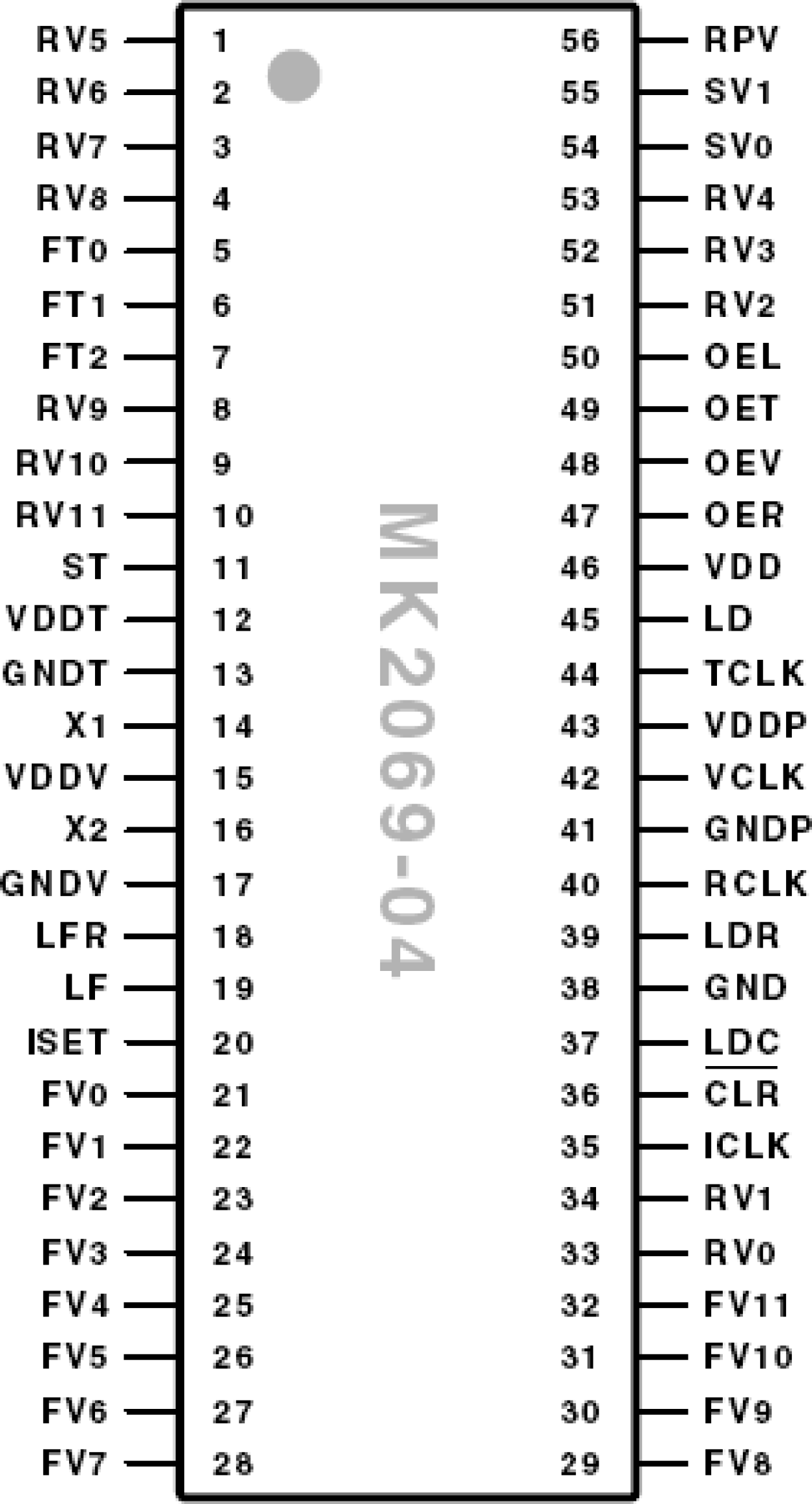

The MK2069-04 is a VCXO (Voltage Controlled Crystal Oscillator) based clock generator that features a PLL (Phase-Locked Loop) input reference divider and feedback divider that have a wide numeric range selectable by the user. This enables a complex PLL multiplication ratio that can be used for translation between clock frequency standards. The on-chip VCXO produces a stable, low jitter output clock using a phase detector frequency down to 8 kHz or lower. This means the MK2069-04 can translate between clock frequencies that have a low common denominator, such as the 8 kHz frame clock common with telecom standards. The MK2069-04 also provides jitter attenuation of the input clock and can accept a low input frequency as well. The device is optimized for user configurability by providing access to all major PLL divider functions. No power-up programming is needed as configuration is pin selected. External VCXO loop filter components provide an additional level of user configurability. The MK2069-04 includes a lock detector (LD) output that serves as a clock status monitor. The clear (CLR) input enables rapid synchronization to the phase of a newly selected input clock.