封装信息

| CAD 模型: | View CAD Model |

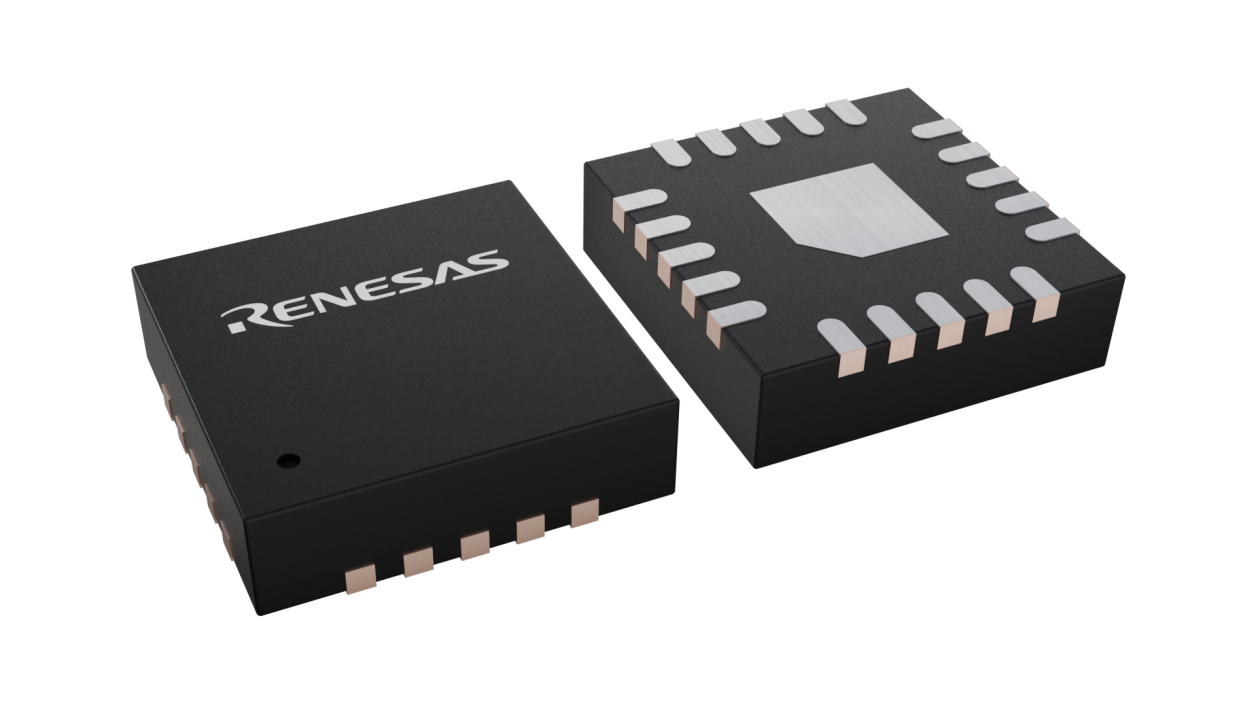

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NDG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 3.0 x 3.0 x 1.0 |

| Pitch (mm): | 0.4 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Pkg. Type | VFQFPN |

| Lead Count (#) | 20 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 624 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 105°C |

| Additive Jitter | 3.4fs |

| Additive Phase Jitter Typ RMS (fs) | 30 |

| Adjustable Phase | No |

| Advanced Features | Flexible Startup Sequencing, Loss of Signal Indicator, Power Down Tolerant, Automatic Clock Parking |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3, PCIe Gen4, PCIe Gen5, PCIe Gen6, PCIe Gen7 |

| Architecture | Common, SRIS, SRNS |

| Channels (#) | 2 |

| Core Voltage (V) | 3.3V |

| Diff. Inputs | 1 |

| Diff. Output Signaling | LP-HCSL |

| Diff. Outputs | 2 |

| Family Name | RC19 |

| Function | Fanout Buffer |

| Input Freq (MHz) | 1 - 400 |

| Input Type | LVDS, HCSL |

| Inputs (#) | 1 |

| Lead Compliant | Yes |

| Length (mm) | 3 |

| Longevity | 2040 四月 |

| MOQ | 624 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 1 - 400 |

| Output Impedance | 85, 100 |

| Output Skew (ps) | 30 |

| Output Type | LP-HCSL |

| Output Voltage (V) | 0.8V |

| Outputs (#) | 2 |

| Pitch (mm) | 0.4 |

| Pkg. Dimensions (mm) | 3.0 x 3.0 x 1.0 |

| Power Consumption Typ (mW) | 72 |

| Supply Voltage (V) | 3.3 - 3.3 |

| Tape & Reel | No |

| Thickness (mm) | 1 |

| VOUT Amplitude Control | No |

| VOUT Slew-rate Control | Yes |

| Width (mm) | 3 |

| 已发布 | No |

有关 RC19002 的资源

描述

The RC19002 is a 2-output PCIe Gen7 buffer that is backward compatible with earlier PCIe generations. The RC19002 provides ultra-low additive jitter and reduced in-to-out delay performance for better design margin and incorporates several features for easier and more robust design.