封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | FCCSP |

| Pkg. Code: | AVG240 |

| Lead Count (#): | 240 |

| Pkg. Dimensions (mm): | 13.5 x 8.7 x 0.9 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | FCCSP |

| Lead Count (#) | 240 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 3000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e1 SnAgCu |

| Temp. Range (°C) | 0 to 70°C |

| Function | DDR5 Gen 3.0 Server RCD |

| Input Voltage Range (V) | 1.06 - 1.16 |

| Length (mm) | 13.5 |

| MOQ | 3000 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 13.5 x 8.7 x 0.9 |

| Reel Size (in) | 13 |

| Supply Voltage (V) | 1.06 - 1.16 |

| Tape & Reel | Yes |

| Thickness (mm) | 0.9 |

| Width (mm) | 8.7 |

有关 RG5R364 的资源

描述

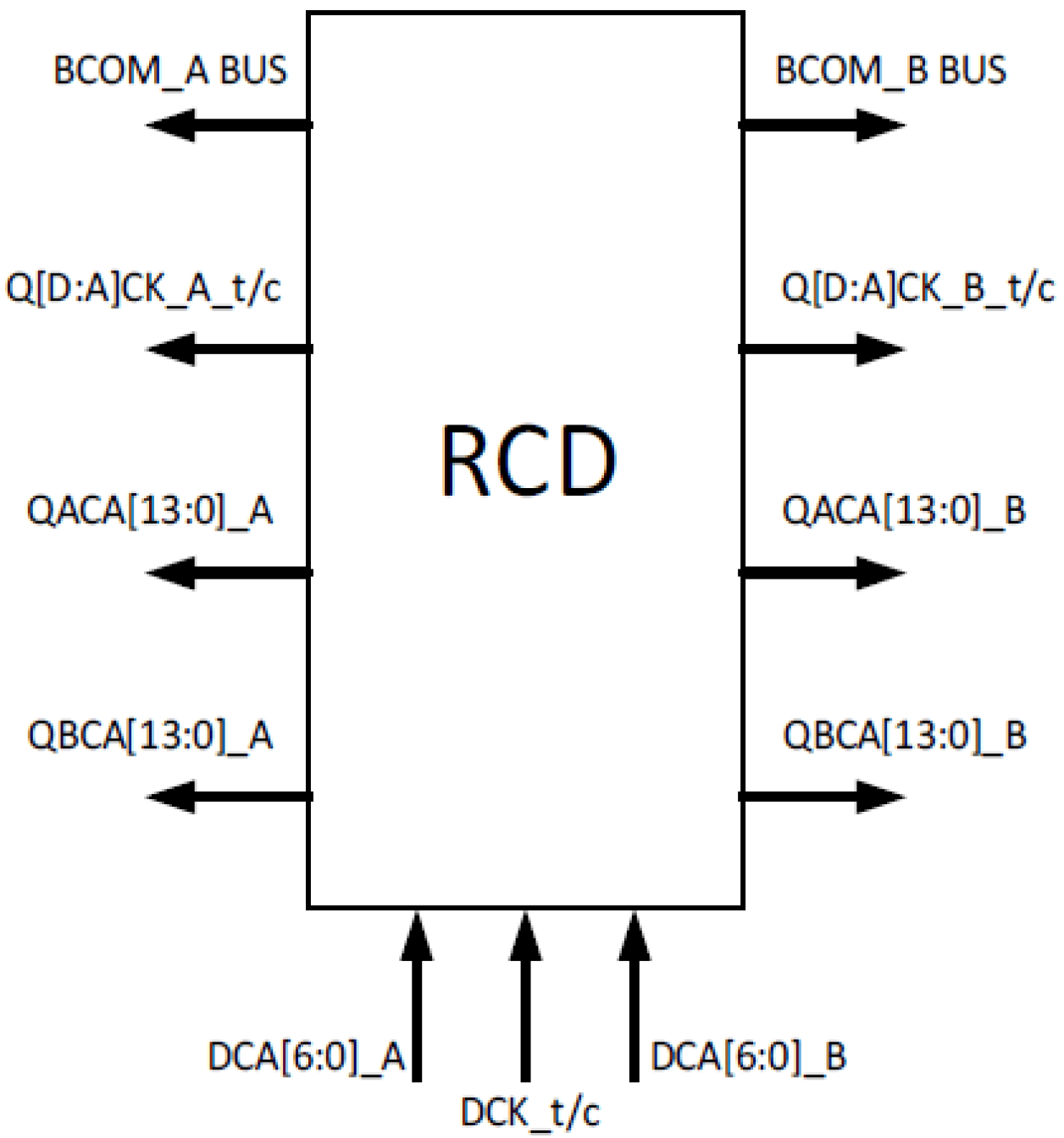

RG5R364(第 3 代 RCD)是用于 DDR5 RDIMM 的寄存时钟驱动器, 在服务器应用中支持高达 6400 MT/s 速率。 其主要功能是缓冲主控制器和 DRAM 之间的命令地址 (CA) 总线、芯片选择和时钟信号。

RG5R364 支持双通道架构,这两个通道具有一些通用逻辑但在其他方面独立运行(例如时钟信号)。 每个通道都有一个 7 位双路数据速率 CA 总线输入、一位单路奇偶校验输入、两位芯片选择信号输入,并会产生两组14 位单数据速率 CA 总线输出和两组芯片选择输出。 RCD 具有一个通用时钟输入和 PLL,但也会向 DRAM 通道产生单独的时钟输出。