概览

描述

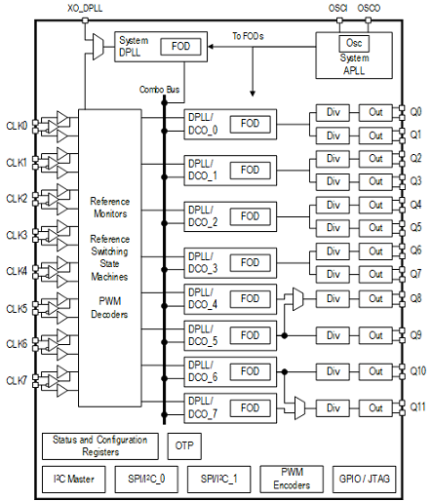

The 8A34001 system synchronizer for IEEE 1588 generates ultra-low jitter, precision timing signals based on the IEEE 1588 Precision Time Protocol (PTP) and Synchronous Ethernet (SyncE). The device can be used as a single timing and synchronization source for a system or two of these devices can be used as a redundant pair for improved system reliability. Digitally Controlled Oscillators (DCOs) are available to be controlled by IEEE 1588 clock recovery servo software running on an external processor. The device supports physical layer timing with Digital PLLs (DPLLs) and other timing blocks necessary to implement a Synchronous Equipment Timing Source (SETS) for SyncE. The DCOs can be controlled using IEEE 1588 information alone, or they can combine IEEE 1588 time information with physical layer frequency information from SyncE in accordance with ITU-T G.8273.2. The 8A34001 can be used to actively measure and compensate for clock propagation delays across backplanes and across circuit boards to ensure the distribution of accurate time and phase with minimal time error between IEEE 1588 Time Stamp Units (TSUs) in a system. The device supports multiple independent channels that control IEEE 1588 clock synthesis, SyncE clock generation, jitter attenuation, and universal frequency translation. Input-to-input, input-to-output and output-to-output phase skew can all be precisely managed. The device outputs ultra-low jitter clocks that can directly synchronize SerDes running at up to 28Gbps; as well as CPRI/OBSAI, SONET/SDH and PDH interfaces and IEEE 1588 TSUs.

To see other devices in this product family, visit the ClockMatrix™ Timing Solutions page.

To easily implement synchronization in IEEE 1588 systems, Renesas offers PTP Clock Manager Software for free under license.

特性

- Eight independent timing channels

- Jitter output below 150fs RMS (typical)

- Digital PLLs (DPLLs) lock to any frequency from 0.5Hz to 1GHz

- DPLLs/Digitally Controlled Oscillators (DCOs) generate any frequency from 0.5Hz to 1GHz

- DCO outputs can be aligned in phase and frequency with the outputs of any DPLL or DCO

- DPLLs comply with ITU-T G.8262 for Synchronous Ethernet (SyncE)

- IEEE 1588 Support:

- DCOs can be controlled by external IEEE 1588 software to synthesize Precision Time Protocol (PTP)/IEEE 1588 clocks with frequency resolution less than 1.11x10-16

- Combo Bus simplifies compliance with ITU-T G.8273.2

- Precise (1ps) resolution for phase measurement and control

- All outputs/inputs can be configured to decode/encode PWM clock signals

- PWM can be used to transmit and receive embedded frame and sync pulses; as well as Time of Day (ToD) and other data

- Device requires a crystal oscillator or fundamental-mode crystal: 25MHz to 54MHz

- Optional XO_DPLL input allows a wider range for XO, TCXO, or OCXO frequencies from 1MHz to 150MHz for applications that require a local oscillator with high stability

- Serial processor ports support 1MHz I²C or 50MHz SPI

产品对比

应用

设计和开发

软件与工具

软件与工具

| Software title

|

Software type

|

公司

|

|---|---|---|

| PTP Clock Manager for Linux 支持 IEEE 1588 和同步以太网通信要求。 PTP Clock Manager 具备时钟伺服和数据包延迟变化 (PDV) 滤波器,可满足 ITU-T 标准 G.8273.4 和 G.8263 的需求。

|

Protocol Stack | 瑞萨电子 |

| Timing Commander Timing Commander™ 是一个基于 Windows™ 的创新软件平台,通过这个平台,系统设计工程师可以通过直观且灵活的图形用户界面 (GUI) 对精密的计时设备进行配置、编程和监控。

|

Code Generator | 瑞萨电子 |

2 项目

|

||

开发板与套件

Evaluation Kit for 8A34001 ClockMatrix

This is the evaluation kit for the Renesas 8A34001 ClockMatrix System Synchronizer for IEEE 1588. The 8A34001 provides eight independent timing channels that can be configured as Digital PLLs (DPLLs) or as Digitally Controlled Oscillators (DCOs). The DPLL channels meet synchronous Ethernet...

模型

ECAD 模块

点击产品选项表中的 CAD 模型链接,查找 SamacSys 中的原理图符号、PCB 焊盘布局和 3D CAD 模型。如果符号和模型不可用,可直接在 SamacSys 请求该符号或模型。

产品选项

当前筛选条件

视频和培训

Introducing the IDT ClockMatrix™ family of devices - high-performance, precision timing solutions designed to simplify clock designs for applications with up to 100 Gbps interface speeds.

They can be used anywhere in a system to perform critical timing functions, such as clock generation, frequency translation, jitter attenuation and phase alignment. A range of devices in the family support BBU, OTN, SyncE, synthesizer and jitter attenuator applications with several density options for each.

For more information, visit the ClockMatrix™ Timing Solutions page.