降低成本的设计注意事项

设计人员一直在寻找降低系统成本的方法,同时继续保持或增强功能。 与此同时,市场对扩展功能和更短产品周期的需求,也给MCU行业带来了新的挑战。 平衡这些相互冲突的需求需要创新的系统设计方法。

降低成本的一种有效策略是通过减少元件数量和使用更具成本效益的 IC 来简化系统架构。 但是,任何更改都必须确保系统功能保持不变,理想情况下还应有所提升。

降低系统成本的挑战

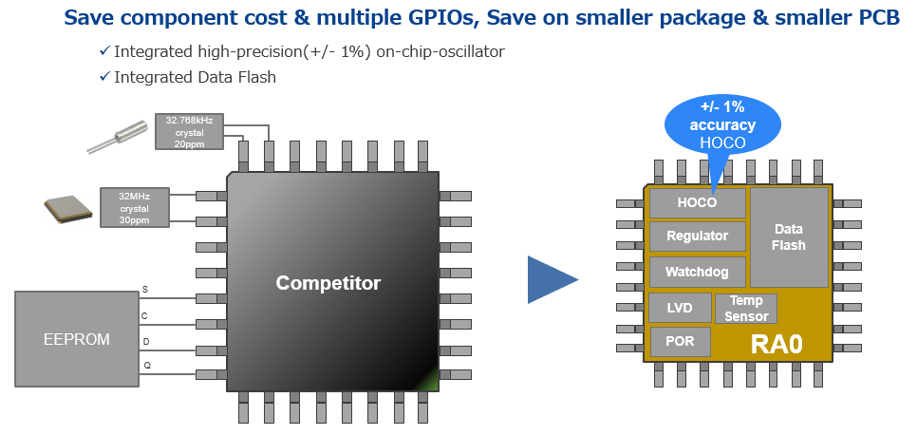

降低成本的一种方法是消除外部元件,例如用片上振荡器代替外部振荡器,或者用嵌入式数据闪存代替外部 EEPROM。 这可以通过减少元件数量和电路板尺寸来降低系统成本。 此外,它还释放了额外的引脚,可以将其重新分配给其他功能。

但是,这些优化带来了技术挑战。 例如,UART 通信通常需要时钟频率误差在2% 到 3%以内,以确保可靠的数据传输。 如果一个通信设备的频率误差为 2%,则 MCU 必须保持 1% 或更低的误差范围,以保持在 3% 的总限制内。 许多低端 MCU 并未配备此类高精度振荡器,即使数据表中提供了规格,它们也可能需要外部电阻器进行调谐。 同样,具有类似 EEPROM 的嵌入式存储器的低端 MCU 也没有得到广泛应用。

RA0E2 MCU 的优势

RA0E2 MCU 有效地解决了这些挑战。 它具有一个片上高速振荡器,在所有工作温度(-40 °C 至 125 °C)下保证 ±1%最大误差。 此外,它还集成了 Data Flash,无需外部 EEPROM。 这些特性可以减少元件数量,从而降低系统成本并简化设计。 此外,释放的引脚可用于 GPIO 或其他功能,在相同的封装尺寸内提供更大的灵活性。

快速原型设计

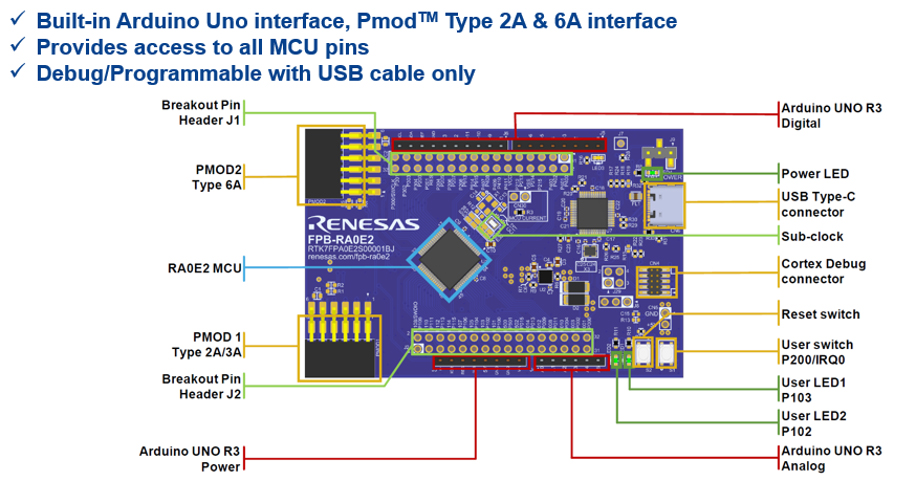

为了加速 RA0E2 MCU 的开发,我们提供了快速原型板 (FPB)。 该评估板旨在简化评估过程,使设计人员能够更高效地开发和测试原型产品。

总结

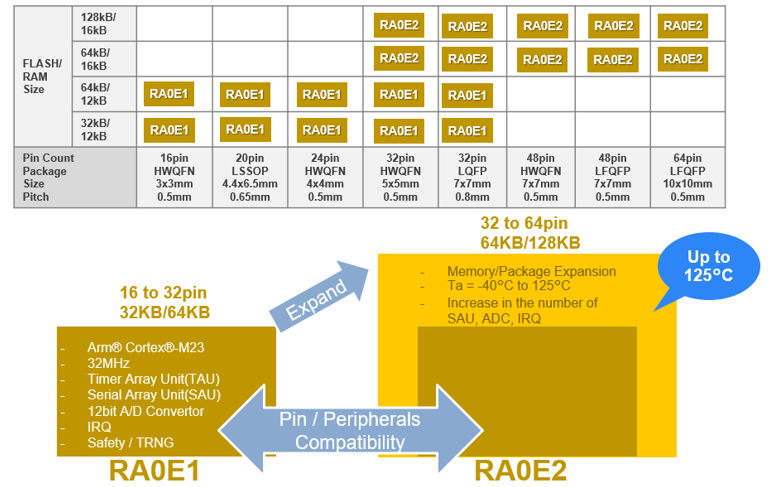

RA0E2 MCU 系列提供有价值的功能,可帮助设计人员在不牺牲性能的情况下降低成本。 RA0 系列与之前发布的 RA0E1 MCU 一起,提供一系列 ROM 大小(32kB 至 128kB)和引脚数选项(16 至 64 引脚),使其适用于各种应用。 此外,FPB-RA0E2 评估板为快速原型设计提供了经济实惠的解决方案,进一步简化了开发过程。

有关 RA0E1 和 RA0E2 特性和优势的更多详细信息,请访问 renesas.com/ra0e1 和 renesas.com/ra0e2。

有关评估板的更多信息,请访问 renesas.com/fpb-ra0e2。