FemtoClock™ 3 无线 (3W) 有两个主要应用:一个是 有线通信中224G PAM SerDes 参考时钟, 另一个是无线通信中“5G Advanced”无线电单元或小型蜂窝。

由于最近 GPU farm/AI 节点的增加,Gen AI 的所有网络速度都将从 112G PAM4 Serdes 转移到 224G PAM4 SerDes(从 800G 到 1.6T)。 多家以太网芯片供应商 – Broadcom、Nvidia、Marvell 和 Cisco 将很快在市场上推出以太网交换机芯片组解决方案,超低抖动时钟解决方案对他们来说变得至关重要。 FemtoClock 3W (RC38312A) 针对此应用。

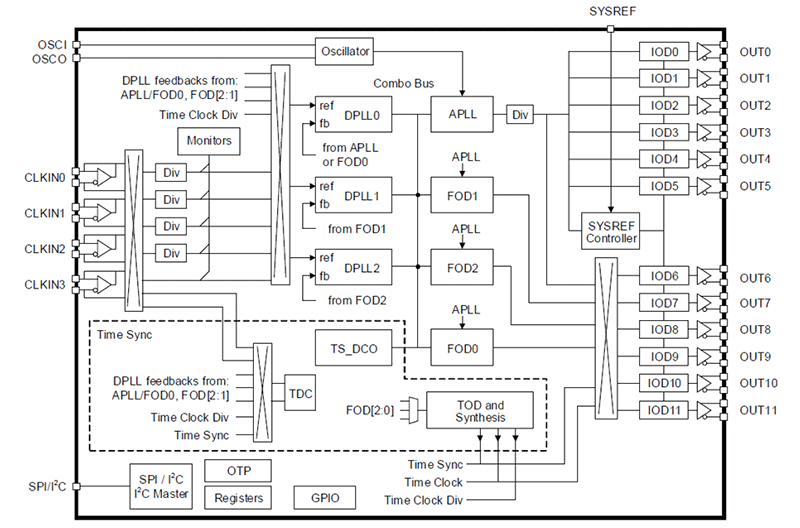

RC38312A 功能

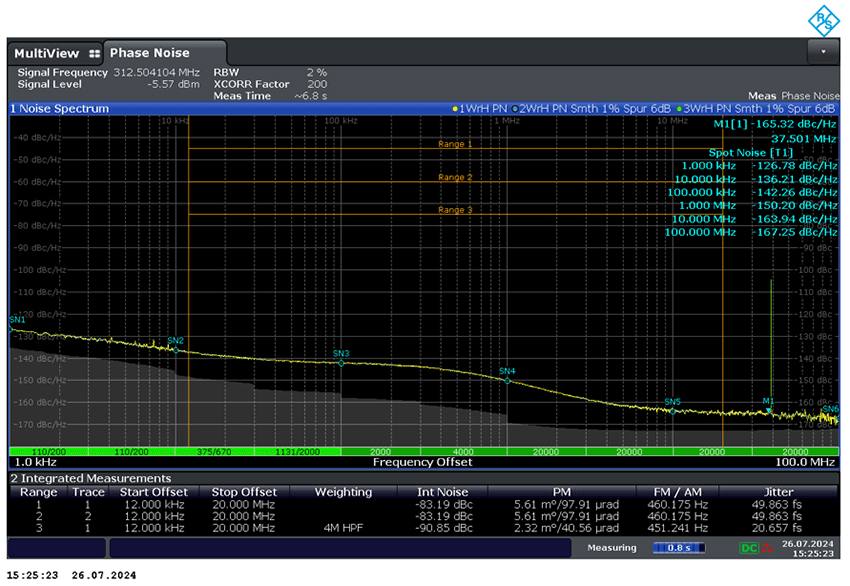

- 超低相位噪声合成器,12kHz 至 20MHz 区间的RMS jitter低于 25fs RMS,在4MHz HPF条件下获得

- 3 个 DPLL 和 3 个 FOD,支持 4 个频域

- 支持 JESD204B/C

- 12 个时钟输出,带独立整数分频器:

- 8:LVDS、HCSL (AC-LVPECL) 或 CML

- 4:LVDS、HCSL (AC-LVPECL) 或 LVCMOS

- 输出频率范围:

- CML:DC to 2.5GHz

- LVDS 或 HCSL:DC to 1GHz

- LVCOMS:DC to 250MHz

- 4 个差分或 8 个单端时钟输入

- 可采用 1.8V 单电源供电

- 功耗小于 1.5W

224G PAM4 SerDes 的时钟要求

224G PAM4 SerDes 的时钟要求非常严格,而 FemtoClock 3W 可以满足这些要求。 224G PAM4 的抖动要求低于 25fs(12kHz 至 20MHz),在4MHz HPF条件下, FemtoClock 3W 有充分的裕量满足该要求。

支持有线和无线的时钟应用

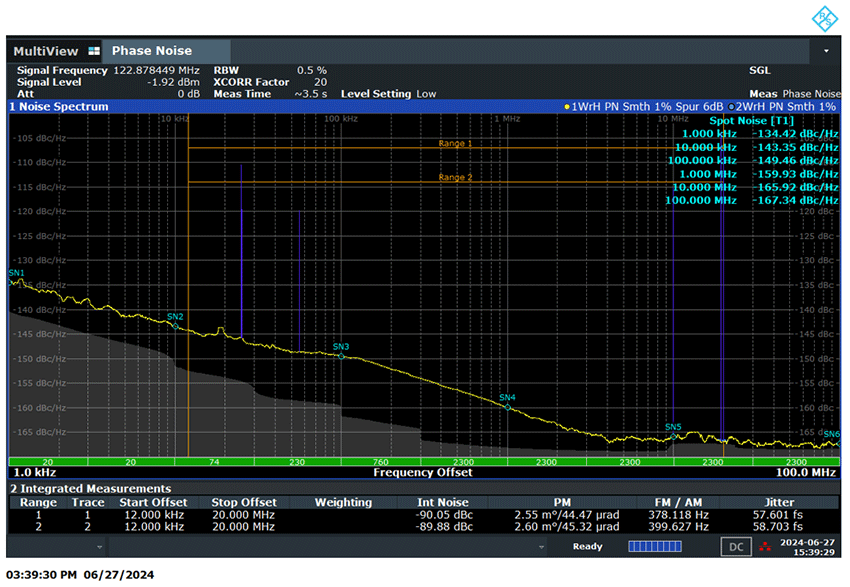

RF 频率合成器是当代先进的通信技术软件定义无线电系统中的重要组件。 这些合成器的频谱纯净度至关重要,因为它直接影响可实现的最大数据速率和信噪特性。 在 RF 应用中,频率合成器必须提供具有宽调谐范围和精确频率分辨率的高频时钟。 要达到这些苛刻的性能标准,不仅需要有限的功耗和紧凑的芯片面积,还需要最小的杂散和相位噪声。

在实际的 1024-QAM 应用中,您可以了解抖动对图的影响。 该协议仍然有助于减少错误。 在商用 SDR 通信系统中,最佳时钟抖动性能是赢得顶级客户业务的关键。 它会影响传输距离和数据速率。

高级架构

在 4G 无线电设计中,PLL 系统使用外部 VCXO 提供低抖动时钟解决方案,JESD204B/C 由 PLL 和 FPGA 实现。 复杂性和成本是触发创新的关键因素,而同步使用的是另一个 DPLL。 它使定时系统带有同步 DPLL、FPGA 和带有外部 VCXO 的双环路抖动衰减器,总共 4 个组件。

在当代无线射频设计中,FemtoClock 3W 进行了改进,包括支持低相位噪声 PLL 的单芯片、3 DPLL、3 小数输出分频器 (FOD)、Combo总线、SYSREF/JESD204B/C 引擎和用于同步应用的 TimeSync 模块。

用于无线射频应用的超低相位噪声

如前所述,相位噪声对于毫米波无线射频应用至关重要。 FemtoClock 3W 基于 BGA 封装(低串扰)、低相位噪声 PLL (Kronos PLL)、最高2.5GHz CML 输出(高频输出通道)、相位调整和补偿而设计。

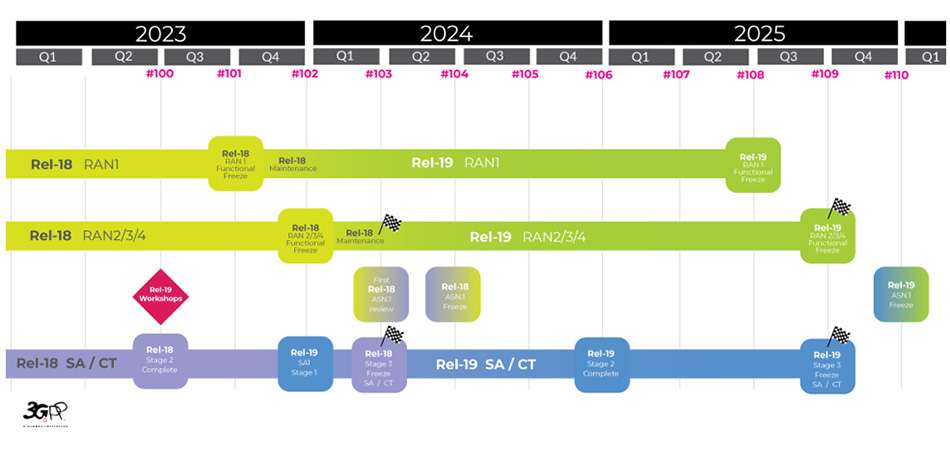

3GPP 时间表

Rel-19 内容是在 2023 年 12 月的 TSG (#102) 上决定的,对于定义“5G-Advanced”的客户来说至关重要。

资料来源:https://www.3gpp.org/specifications-technologies/releases/release-19

结论

FemtoClock 3W 是瑞萨电子最新的 PLL 技术,支持无线和有线应用。 采用单个 1.8V 电源,提供最低的功耗和超低相位抖动时钟输出。

FemtoClock 3W 是无线射频单元和 1.6T 以太网交换机的 224G PAM4 SerDes 参考时钟的最佳时钟解决方案。

要开始评估 FemtoClock 3W,请立即获取评估套件!